Спец курс (Избранные главы VHDL)/Верификация описания — различия между версиями

Материал из Wiki

Vidokq (обсуждение | вклад) (→Слайд:События) |

Vidokq (обсуждение | вклад) (→Слайд:Главный модуль) |

||

| Строка 97: | Строка 97: | ||

[[Файл:Операции.png]] | [[Файл:Операции.png]] | ||

| − | ===Слайд:Главный модуль=== | + | ===Слайд:Главный модуль MAIN=== |

{{Гол|'''<big>Описание на языке C++</big>'''}} | {{Гол|'''<big>Описание на языке C++</big>'''}} | ||

<source lang="cpp"> | <source lang="cpp"> | ||

| Строка 116: | Строка 116: | ||

} | } | ||

</source> | </source> | ||

| + | |||

| + | ===Слайд: Модуль === | ||

| + | <source lang="cpp"> | ||

| + | #include <systemc.h> | ||

| + | SC_MODULE(module_name) { | ||

| + | MODULE_BODY | ||

| + | };</source> | ||

| + | Содержит: | ||

| + | * '''{{Фио|<big>Порты</big>}}''' | ||

| + | * '''{{Фио|<big>Каналы связи</big>}}''' | ||

| + | * '''{{Фио|<big>Объявления переменных для хранения данных</big>}}''' | ||

| + | * '''{{Фио|<big>Другие модули с большей вложенностью</big>}}''' | ||

| + | * '''{{Фио|<big>Конструктор</big>}}''' | ||

| + | * '''{{Фио|<big>Деструктор</big>}}''' | ||

| + | * '''{{Фио|<big>Функции -процессы</big>}}''' | ||

| + | * '''{{Фио|<big>Вспомогательные функции</big>}}''' | ||

| + | |||

| + | ===Слайд: Конструктор (SC_CTOR)=== | ||

| + | <source lang="cpp">SC_CTOR(module_name) | ||

| + | : Initialization // OPTIONAL | ||

| + | { | ||

| + | Subdesign_Allocation | ||

| + | Subdesign_Connectivity | ||

| + | Process_Registration | ||

| + | Miscellaneous_Setup | ||

| + | }</source> | ||

| + | |||

| + | * '''{{Фио|<big>Объявление под модулей</big>}}''' | ||

| + | * '''{{Фио|<big>Подключение и соединение с подмодулями</big>}}''' | ||

| + | * '''{{Фио|<big>Регистрация процессов на SystemC</big>}}''' | ||

| + | * '''{{Фио|<big>Обеспечение постоянной чувствительности</big>}}''' | ||

| + | * '''{{Фио|<big>Разнообразные пользовательские объявления</big>}}'' | ||

| + | |||

| + | ===Слайд: Конструктор (SC_HAS_PROCESS)=== | ||

| + | <source lang="cpp"> | ||

| + | //FILE: module_name.h | ||

| + | SC_MODULE(module_name) { | ||

| + | SC_HAS_PROCESS(module_name); | ||

| + | module_name(sc_module_name instname[, other_args…]) | ||

| + | : sc_module(instname) | ||

| + | [, other_initializers] | ||

| + | { | ||

| + | CONSTRUCTOR_BODY | ||

| + | } | ||

| + | };</source> | ||

| + | |||

| + | * '''{{Фио|<big>Все возможности конструктора SC_CTOR</big>}}''' | ||

| + | * '''{{Фио|<big>Альтернативный метод создания модуля</big>}}''' | ||

| + | * '''{{Фио|<big>Позволяет создавать конструктор с аргументами(+ к имени модуля)</big>}}''' | ||

| + | * '''{{Фио|<big>Используется, если желаете расположить конструктор в файле описания .cpp (не в файле .h)</big>}}''' | ||

| + | |||

| + | ===Слайд: Процесс SC_THREAD === | ||

| + | |||

| + | <source lang="cpp"> | ||

| + | SC_MODULE(simple_process_ex) { | ||

| + | SC_CTOR(simple_process_ex) { | ||

| + | SC_THREAD(my_thread_process); | ||

| + | } | ||

| + | void my_thread_process(void); | ||

| + | };</source> | ||

| + | |||

| + | {{Зел|'''SC_THREAD'''}} в '''SystemC''': | ||

| + | # аналог {{Зел|'''initial block'''}} в '''Verilog''' | ||

| + | # {{Зел|'''process'''}} без списка чувствительности с оператором '''wait()''' в '''VHDL'''. | ||

===Слайд:Иерархия и структура проекта=== | ===Слайд:Иерархия и структура проекта=== | ||

Версия 15:35, 14 ноября 2012

- Заголовок

- Верификация описания.

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Верификация описания

- Дополнительный нижний колонтитул

- Зайцев В.С., 13:16, 2 декабря 2013

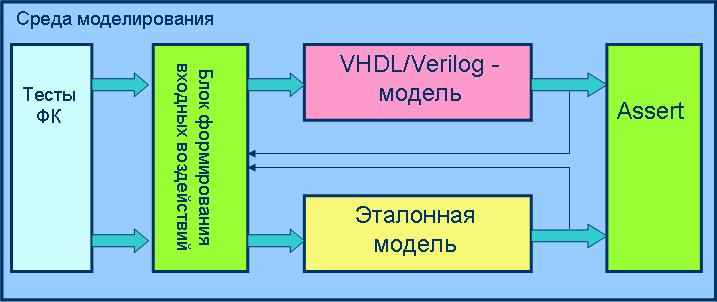

Слайд:Верификация описания

Слайд:Верификация описания:step

- Среда моделирования

- Active-HDL™

- Riviera-PRO™

- NC-Sim®

- ModelSim®

- QuestaSim®

- VCS-MX®

- Структура проекта

- Тестовое окружение

- RTL-модель (Verilog,VHDL)

- Эталонная модель (SystemC)

- Assert'ы (psl, OVVM, UVM)

- Отчеты и базы по результатам моделирования

Слайд:Эталонная модель на языке SystemC

- Высокий уровень абстракции

- Скорость моделирования

- Возможности языка C++

- Инструменты для автоматизации

- Совместное моделирование с другими HDL-языками

Основы языка SystemC

Слайд:Типы данных (Форматы и способ представления данных)

Слайд:Типы данных (native)

// Пример типа данных C++ int spark_offset; unsigned repairs = 0 ; // Count repair unsigned long mileage; // Miles driven short int speedometer; // -20.. 0.. 100 MPH float temperature; // Engine temp in C double time_of_last_request; //Time of bus std:: string license_plate; // Text for license const bool WARNING_LIGHT = true; // Status enum compass {SW,W,NW,N,NE,E, SE, S} ;

Слайд:Типы данных (Arithmetic)

// Пример целочисленных типов данных C++ sc_int<LENGTH> NAME...; sc_uint<LENGTH> NAME...; sc_bigint<BITWIDTH> NAME...; sc_biguint<BITWIDTH> NAME...; // SystemC integer data types sc_int<5> seat_position=3; //5 bits: 4 plus sign sc_uint<13> days_SLOC(4000); //13 bits: no sign sc_biguint<80> revs_SLOC; // 80 bits: no sign

Слайд:Типы данных (Boolean)

// Пример типа данных SystemC sc_bit NAME...; sc_bv<BITWIDTH> NAME...;

- sc_bit и sc_bv могут принимать значения: SC_LOGIC_1 и SC_LOGIC_0.

- Для сокращения типов, можно использовать Log_1 и Log_0 или ‘1’ и ‘0’.

- Над этим типом данных возможно выполнение битовых операций and, or, xor (&,|, ^).

- Для обращения к отдельным битам и массивам [], range().

sc_bit flag(SC_LOGIC_1); // more efficient to use bool sc_bv<5> positions = "01101"; sc_bv<6> mask = "100111"; sc_bv<5> active = positions & mask;// 00101 sc_bv<1> all = active. and_reduce (); // SC_LOGIC_0 positions. range (3,2) = "00"; // 00001 positions [2] = active[0] ^ flag;

Слайд:Типы данных (Несколько значений )

// Пример типа данных SystemC sc_logic NAME[,NAME]...; sc_lv<BITNIDTH> NAME[,NAME ]...; sc_logic buf(sc_dt::Log_Z); sc_lv<8> data_drive ("zz01XZ1Z"); data_drive.range (5,4) = "ZZ";// ZZZZXZ1Z buf = '1';

Слайд:Операторы SystemC

Слайд:Главный модуль MAIN

Описание на языке C++

int main(int argc, char* argv[]) { BODY_OF_PROGRAM return EXIT_CODE; // }

Описание на языке SystemC

int sc_main(int argc, char* argv[]) { //ELABORATION sc_start(); // <-- Simulation begins & ends // in this function! //[POST-PROCESSING] return EXIT_CODE; // }

Слайд: Модуль

#include <systemc.h> SC_MODULE(module_name) { MODULE_BODY };

Содержит:

- Порты

- Каналы связи

- Объявления переменных для хранения данных

- Другие модули с большей вложенностью

- Конструктор

- Деструктор

- Функции -процессы

- Вспомогательные функции

Слайд: Конструктор (SC_CTOR)

SC_CTOR(module_name) : Initialization // OPTIONAL { Subdesign_Allocation Subdesign_Connectivity Process_Registration Miscellaneous_Setup }

- Объявление под модулей

- Подключение и соединение с подмодулями

- Регистрация процессов на SystemC

- Обеспечение постоянной чувствительности

- 'Разнообразные пользовательские объявления

Слайд: Конструктор (SC_HAS_PROCESS)

//FILE: module_name.h SC_MODULE(module_name) { SC_HAS_PROCESS(module_name); module_name(sc_module_name instname[, other_args…]) : sc_module(instname) [, other_initializers] { CONSTRUCTOR_BODY } };

- Все возможности конструктора SC_CTOR

- Альтернативный метод создания модуля

- Позволяет создавать конструктор с аргументами(+ к имени модуля)

- Используется, если желаете расположить конструктор в файле описания .cpp (не в файле .h)

Слайд: Процесс SC_THREAD

SC_MODULE(simple_process_ex) { SC_CTOR(simple_process_ex) { SC_THREAD(my_thread_process); } void my_thread_process(void); };

SC_THREAD в SystemC:

- аналог initial block в Verilog

- process без списка чувствительности с оператором wait() в VHDL.