Спец курс (Избранные главы VHDL)/Верификация описания — различия между версиями

Материал из Wiki

Vidokq (обсуждение | вклад) |

Vidokq (обсуждение | вклад) (→Слайд:Верификация описания) |

||

| Строка 5: | Строка 5: | ||

[[Файл:Функциональная_верификация.mm]] | [[Файл:Функциональная_верификация.mm]] | ||

| + | |||

| + | ==Слайд:Методы верификации проекта== | ||

| + | * {{Сн|'''<big>Имитационная верификация</big>'''}} - верификация с использованием моделирования | ||

| + | * {{Сн|'''<big>Формальная верификация</big>'''}} -проверка модели с целью доказательства ее корректности и эквивалентности спецификации | ||

| + | (Пример: пакет FormulPro ф. MentorGraphics, пакеты фирмы Verplex, www.verplex.com) | ||

| + | |||

==Слайд:Верификация описания== | ==Слайд:Верификация описания== | ||

Версия 11:56, 21 ноября 2012

- Заголовок

- Верификация описания.

- Автор

- Зайцев В.С.

- Нижний колонтитул

- Спец курс (Избранные главы VHDL)/Верификация описания

- Дополнительный нижний колонтитул

- Зайцев В.С., 13:16, 2 декабря 2013

Содержание |

Слайд:Методы верификации проекта

- Имитационная верификация - верификация с использованием моделирования

- Формальная верификация -проверка модели с целью доказательства ее корректности и эквивалентности спецификации

(Пример: пакет FormulPro ф. MentorGraphics, пакеты фирмы Verplex, www.verplex.com)

Слайд:Верификация описания

Слайд:Верификация описания:step

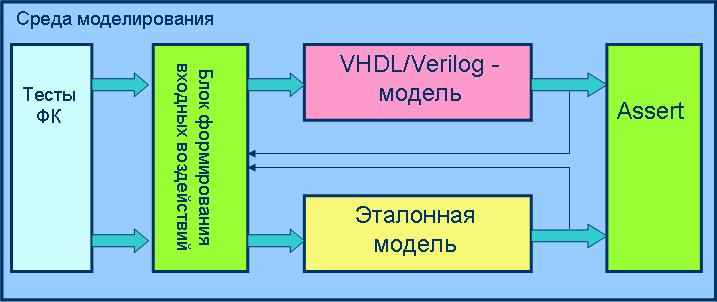

- Среда моделирования

- Active-HDL™

- Riviera-PRO™

- NC-Sim®

- ModelSim®

- QuestaSim®

- VCS-MX®

- Структура проекта

- Тестовое окружение

- RTL-модель (Verilog,VHDL)

- Эталонная модель (SystemC)

- Assert'ы (psl, OVVM, UVM)

- Отчеты и базы по результатам моделирования

Слайд:Эталонная модель на языке SystemC

- Высокий уровень абстракции

- Скорость моделирования

- Возможности языка C++

- Инструменты для автоматизации

- Совместное моделирование с другими HDL-языками