Co-Simulation/Описание микросхемы FT2232H

Материал из Wiki

- Техническое задание

- Описание FT2232H

- Описание FT232H

- (TUMPA) TIAO USB Multi Protocol Adapter

- (TUMPA) Litle

- Описание макета

- Примеры кода

Содержание |

FT2232H - Hi-Speed Dual USB UART/FIFO IC

The FT2232H is FTDI’s 5th generation of USB devices. The FT2232H is a USB 2.0 Hi-Speed (480Mb/s) to UART/FIFO IC. It has the capability of being configured in a variety of industry standard serial or parallel interfaces.

Building on the innovative features of the FT2232, the FT2232H has two multi-protocol synchronous serial engines (MPSSEs) which allow for communication using JTAG, I2C and SPI on two channels simultaneously.

The FT2232H is available in Pb-free (RoHS compliant) 64-pin LQFP and QFN packages.

Product Information

- FT2232H Datasheet

- VCP Drivers

- D2XX Drivers

- MPSSE Code Examples

- LibMPSSE-I2C DLL

- MPSSE JTAG DLL

- MPSSE SPI DLL

Key Hardware Features

- Single chip USB to dual serial / parallel ports with a variety of configurations.

- Entire USB protocol handled on the chip. No USB specific firmware programming required.

- USB 2.0 High Speed (480Mbits/second) and Full Speed (12Mbits/second) compatible.

- Dual Multi-Protocol Synchronous Serial Engine (MPSSE) to simplify synchronous serial protocol (USB to JTAG, I2C, SPI or bit-bang) design.

- Dual independent UART or FIFO ports configurable using MPSSEs.

- Independent Baud rate generators.

- RS232/RS422/RS485 UART Transfer Data Rate up to 12Mbaud. (RS232 Data Rate limited by external level shifter).

- USB to parallel FIFO transfer data rate up to 10Mbyte/sec.

- Single channel synchronous FIFO mode for transfers up to 40 Mbytes/sec.

- CPU-style FIFO interface mode simplifies CPU interface design.

- MCU host bus emulation mode configuration option.

- Fast Opto-Isolated serial interface option.

- FTDI’s royalty-free Virtual Com Port (VCP) and Direct (D2XX) drivers eliminate the requirement for USB driver development in most cases.

- Adjustable receive buffer timeout.

- Option for transmit and receive LED drive signals on each channel.

- Enhanced bit-bang Mode interface option with RD# and WR# strobes.

- FT245B-style FIFO interface option with bidirectional data bus and simple 4 wire handshake interface.

- Highly integrated design includes +1.8V LDO regulator for VCORE, integrated POR function and on chip clock multiplier PLL (12MHz – 480MHz).

- Asynchronous serial UART interface option with full hardware handshaking and modem interface signals.

- Fully assisted hardware or X-On / X-Off software handshaking.

- UART Interface supports 7/8 bit data, 1/2 stop bits, and Odd/Even/Mark/Space/No Parity.

- Auto-transmit enable control for RS485 serial applications using TXDEN pin.

- Operational configuration mode and USB Description strings configurable in external EEPROM over the USB interface.

- Configurable I/O drive strength (4,8,12 or 16mA) and slew rate.

- Low operating and USB suspend current.

- Supports bus powered, self powered and high-power bus powered USB configurations.

- UHCI/OHCI/EHCI host controller compatible.

- USB Bulk data transfer mode (512 byte packets in Hi-Speed mode).

- +1.8V (chip core) and +3.3V I/O interfacing (+5V Tolerant).

- Extended -40°C to 85°C industrial operating temperature range.

- Compact 64-LD Lead Free LQFP or LQFN package.

- +3.3V single supply operating voltage range.

Application Areas

- Single chip USB to dual channel UART (RS232, RS422 or RS485).

- Single chip USB to dual channel FIFO.

- Single chip USB to dual channel JTAG.

- Single chip USB to dual channel SPI.

- Single chip USB to dual channel I2C.

- Single chip USB to dual channel Bit-Bang.

- Single chip USB to dual combination of any of above interfaces.

- Single chip USB to Fast Serial Optic Interface.

- Single chip USB to CPU target interface (as memory), double and independent.

- Single chip USB to Host Bus Emulation (as CPU).

- USB Audio and Low Bandwidth Video data transfer

- PDA to USB data transfer

- USB Smart Card Readers

- USB Instrumentation

- USB Industrial Control

- USB MP3 Player Interface

- USB FLASH Card Reader / Writers

- Set Top Box PC - USB interface

- USB Digital Camera Interface

- USB Bar Code Readers

Блок схема ИС FT2232H

Dual Multi-Purpose UART/FIFO Controllers. The FT2232H has two independent UART/FIFO Controllers. These control the UART data, 245 fifo data, opto isolation (Fast Serial) or control the Bit- Bang mode if selected by SETUP command. Each Multi-Purpose UART/FIFO Controller also contain an MPSSE (Multi Protocol Synchronous Serial Engine) which can be used independently of each other. Using this MPSSE, the Multi-Purpose UART/FIFO Controller can be configured, under software command, to have 1 MPSSE + 1 UART / 245 FIFO (each UART / 245 can be set to Bit Bang mode to gain extra I/O if required) or 2 MPSSE.

USB Protocol Engine and FIFO control. The USB Protocol Engine controls and manages the interface between the UTMI PHY and the FIFOs of the chip. It also handles power management and the USB protocol specification.

Dual Port FIFO TX Buffer (4Kbytes per interface). Data from the Host PC is stored in these buffers to be used by the Multi-purpose UART/FIFO controllers. This is controlled by the USB Protocol Engine and FIFO control block.

Dual Port FIFO RX Buffer (4Kbytes per interface). Data from the Multi-purpose UART/FIFO controllers is stored in these blocks to be sent back to the the Host PC when requested. This is controlled by the USB Protocol Engine and FIFO control block.

RESET Generator – The integrated Reset Generator Cell provides a reliable power-on reset to the device internal circuitry at power up. The RESET# input pin allows an external device to reset the FT2232H. RESET# should be tied to VCCIO (+3.3v) if not being used.

Independent Baud Rate Generators – The Baud Rate Generators provides a x16 or a x10 clock input to the UART‟s from a 120MHz reference clock and consists of a 14 bit pre-scaler and 4 register bits which provide fine tuning of the baud rate (used to divide by a number plus a fraction). This determines the Baud Rate of the UART which is programmable from 183 baud to 12 million baud. The FT2232H does not support the baud rates of 7 Mbaud 9 Mbaud, 10 Mbaud and 11 Mbaud.

See FTDI application note AN232B-05 on the FTDI website (www.ftdichip.com) for more details.

+1.8V LDO Regulator. The +1.8V LDO regulator generates the +1.8 volts for the core and the USB transceiver cell. Its input (VREGIN) must be connected to a +3.3V external power source. It is also recommended to add an external filtering capacitor to the VREGIN. There is no direct connection from the +1.8V output (VREGOUT) and the internal functions of the FT2232H. The PCB must be routed to connect VREGOUT to the pins that require the +1.8V including VREGIN.

UTMI PHY. The Universal Transceiver Macrocell Interface (UTMI) physical interface cell. This block handles the Full speed / High Speed SERDES (serialise – deserialise) function for the USB TX/RX data. It also provides the clocks for the rest of the chip. A 12 MHz crystal should be connected to the OSCI and OSCO pins. A 12K Ohm resistor should be connected between REF and GND on the PCB.

The UTMI PHY functions include:

- Supports 480 Mbit/s “High Speed” (HS)/ 12 Mbit/s “Full Speed” (FS), FS Only and “Low Speed” (LS)

- SYNC/EOP generation and checking

- Data and clock recovery from serial stream on the USB.

- Bit-stuffing/unstuffing; bit stuff error detection.

- Manages USB Resume, Wake Up and Suspend functions.

- Single parallel data clock output with on-chip PLL to generate higher speed serial data clocks.

EEPROM Interface. When used without an external EEPROM the FT2232H defaults to a USB to dual asynchronous serial port device. Adding an external 93C46 (93C56 or 93C66) EEPROM allows each of the chip‟s channels to be independently configured as a serial UART (RS232 mode), parallel FIFO (245) mode or fast serial (opto isolation). The external EEPROM can also be used to customise the USB VID, PID, Serial Number, Product Description Strings and Power Descriptor value of the FT2232H for OEM applications. Other parameters controlled by the EEPROM include Remote Wake Up, Soft Pull Down on Power-Off and I/O pin drive strength.

The EEPROM should be a 16 bit wide configuration such as a Microchip 93LC46B or equivalent capable of a 1Mbit/s clock rate at VCC = +3.00V to 3.6V. The EEPROM is programmable in-circuit over USB using a utility program called MPROG available from FTDI‟s web site (www.ftdichip.com). This allows a blank part to be soldered onto the PCB and programmed as part of the manufacturing and test process.

If no EEPROM is connected (or the EEPROM is blank), the FT2232H will default to dual serial ports. The device uses its built-in default VID (0403) , PID (6010) Product Description and Power Descriptor Value. In this case, the device will not have a serial number as part of the USB descriptor.

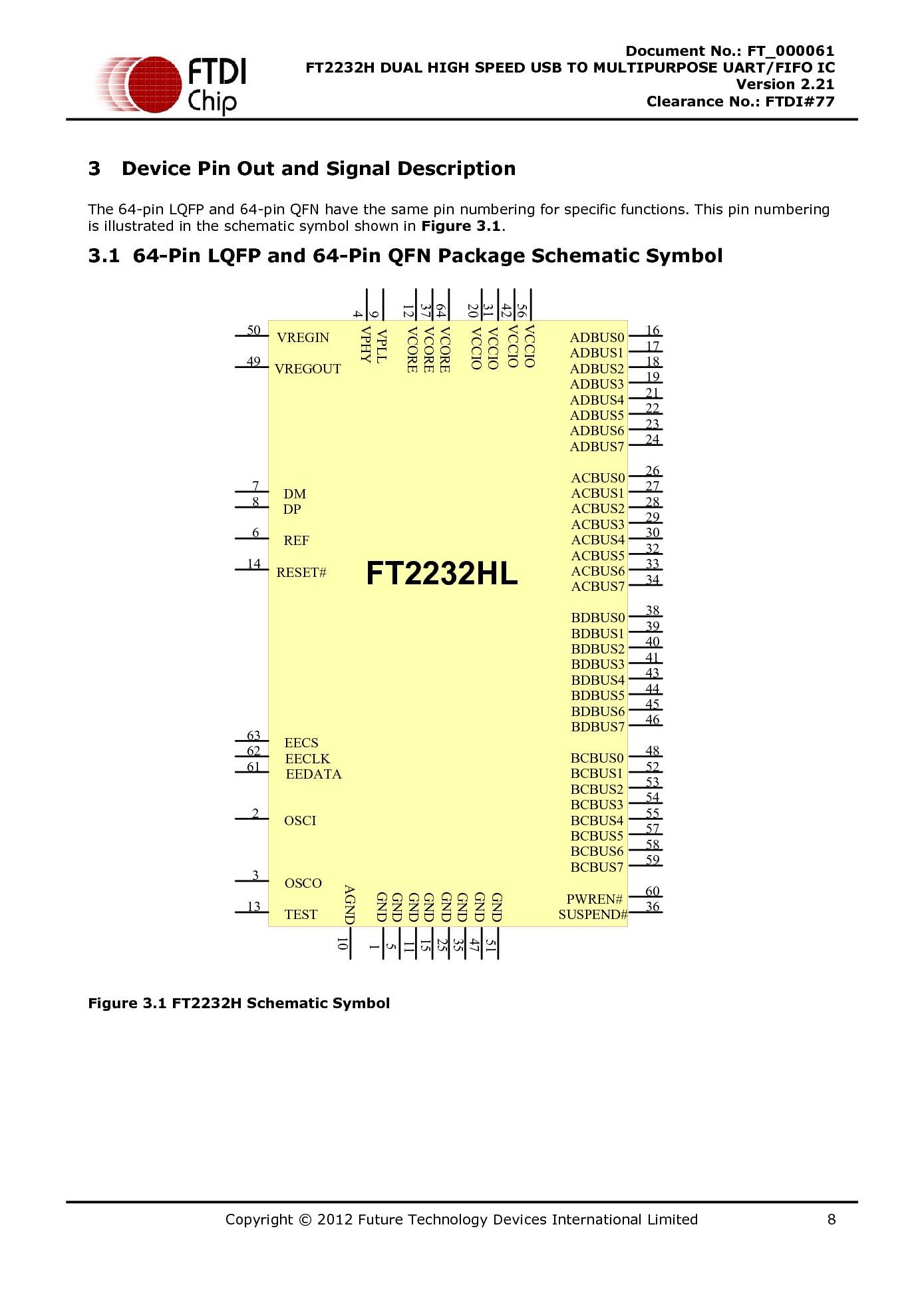

Цоколёвка

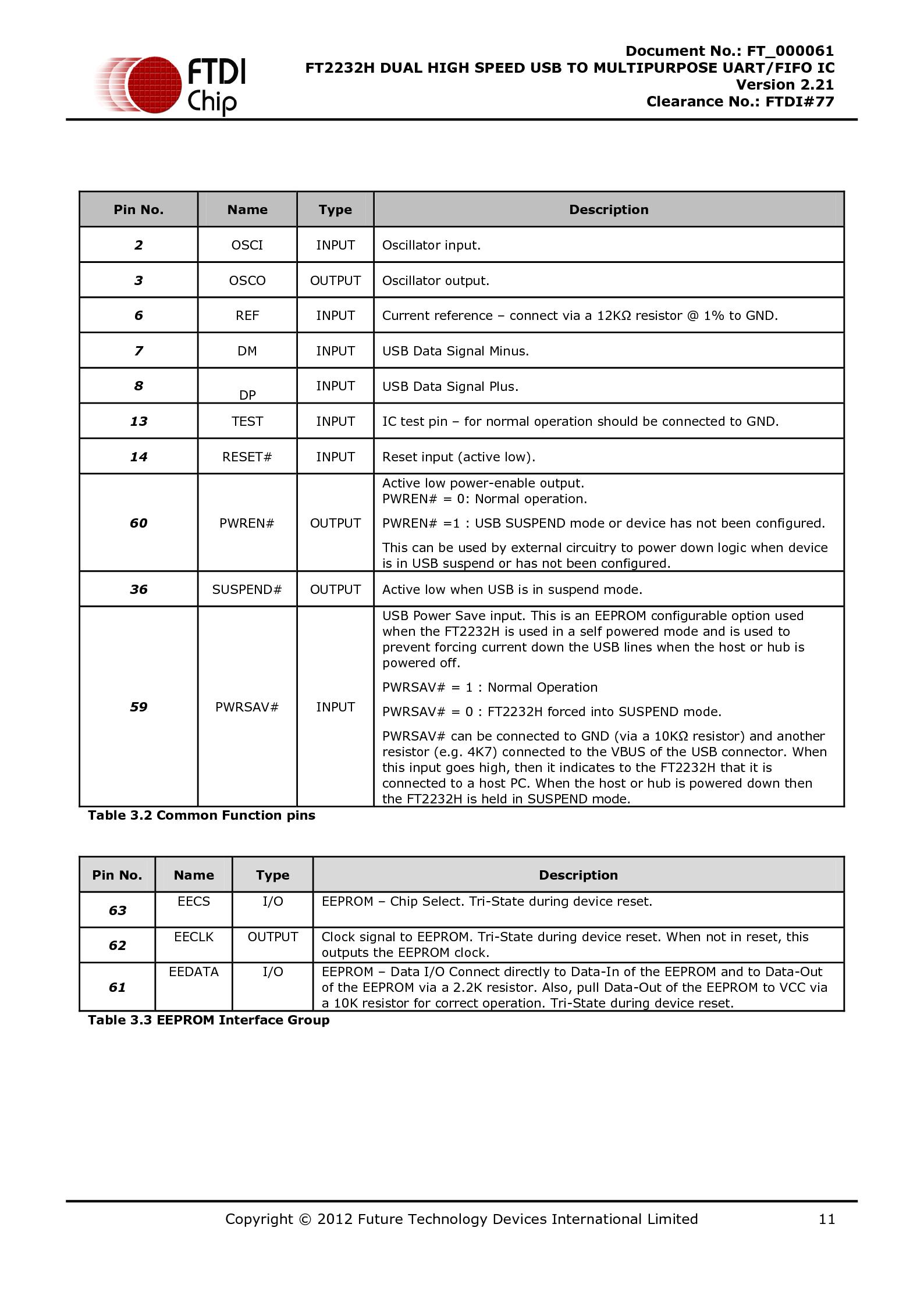

Назначение выводов

3.4.2 FT2232H pins used in an FT245 Style Synchronous FIFO Interface

3.4.7 FT2232H Pins Configured as a CPU-style FIFO Interface

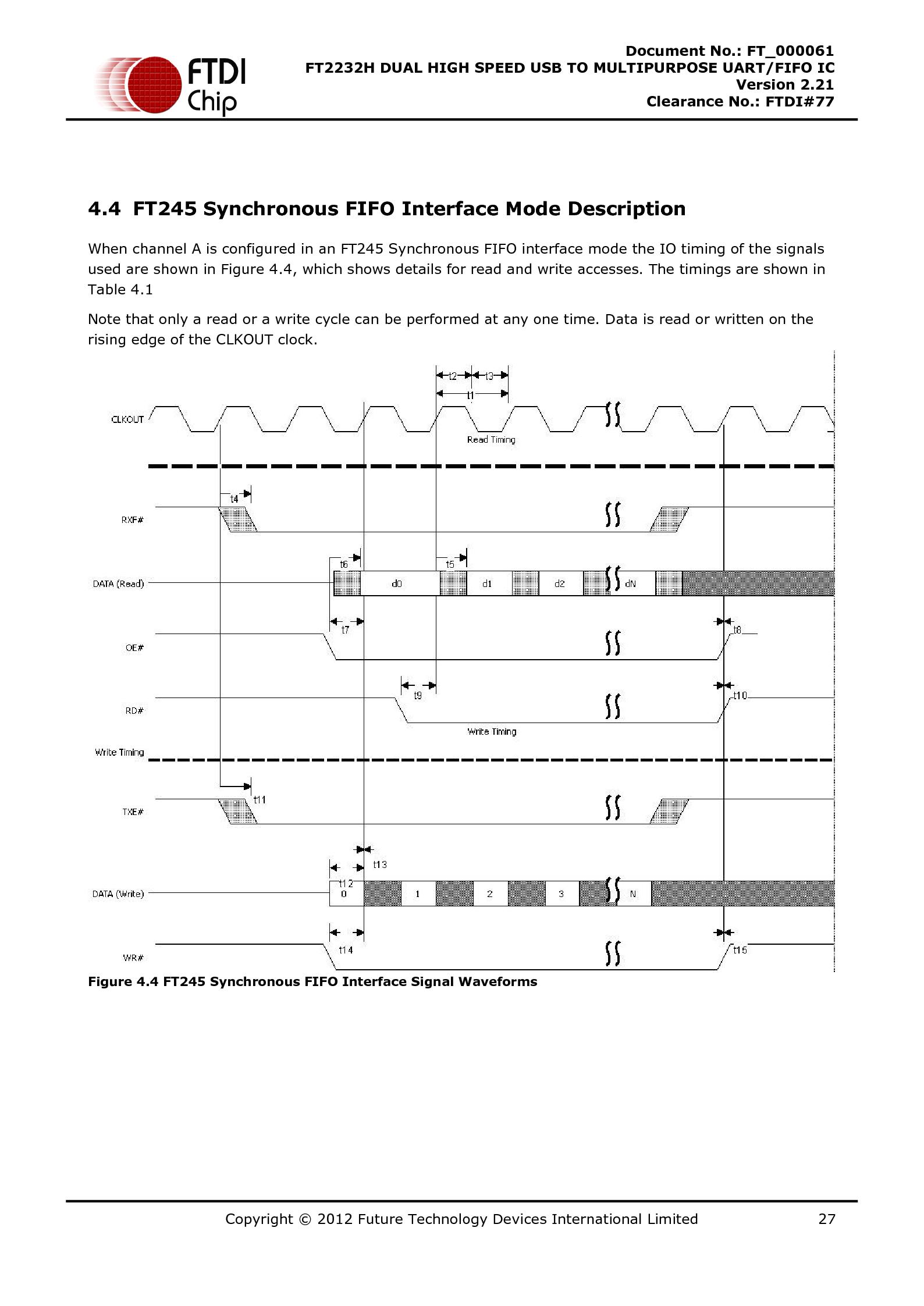

4.4 FT245 Synchronous FIFO Interface Mode Description

4.9 CPU-style FIFO Interface Mode Description

Ссылки

- Документация FT2232H на русском языке

- AN_130_FT2232H_Used_In_FT245 Synchronous FIFO Mode.pdf

- FT2232H USB Avalon Core (opencores.org)