Проектирование цифровых систем на языках описания аппаратуры/Лекция 16

- Заголовок

- Проектирование схем на FPGA

- Автор

- Ланкевич Ю.Ю.

- Нижний колонтитул

- Проектирование цифровых систем на языках описания аппаратуры/Лекция 16

- Дополнительный нижний колонтитул

- Ланкевич Ю.Ю., 03:38, 24 декабря 2020

Слайд:Введение в проектирование схем на ПЛИС

Основные современные типы ПЛИС:

- CPLD – Complex Programmable Logic Devices – сложные программируемые логические устройства;

- FPGA – Field Programmable Array – программируемые пользователем вентильные матрицы.

Слайд: общие сведения о CPLD

Идеей CPLD является реализация нескольких узлов на одном кристалле, добавляя к ним возможности передачи сигналов между узлами. Современные микросхемы CPLD имеют программируемые узлы на основе флеш памяти, т.е. являются многократно программируемыми, и содержат блоки из 18 или 16 триггеров вместе с соответсвующей матрицей вентилей И-ИЛИ. Такие ПЛИС обладают предсказуемыми задержками распространения сигнала (входные сигналы проходят через несложную схему вентелей и коммутационных узлов), пркатически не требуют внешних компонентов и удобны для работы в качестве "glue logic", т.е. микросхем, выполняющих в устройстве сопряжение более сложных устройств и заменяющих на печатной плате множество более простых микросхем, состоящих из нескольких вентелей.

Недостатком архитектуры CPLD является сложность построения более ёмких микросхем. Существующие в настоящее время CPLD состоят из десятков-сотен триггеров и практически не получают преимуществ от перехода к новым технологическим процессам.

Микросхемы с архитектурой CPLD в настоящее время всё ещё выпускаются компанией Xilinx. Это серия CoolRunner-II, которую рассмотрим далее.

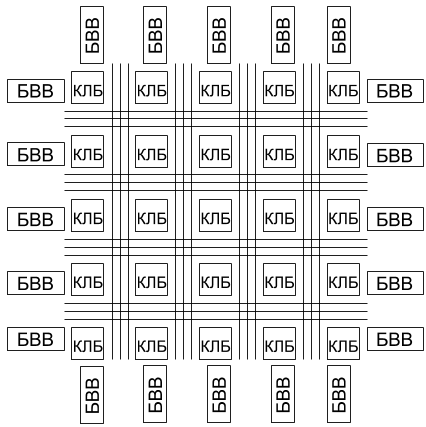

Слайд: общие сведения об FPGA

Программируемые микросхемы с архитектурой FPGA имеют в основе набор конфигурируемых блоков (логических ячеек), содержащих базовые компоненты цифровой логики – логические элементы и триггеры. Отдельные ячейки соединяются друг с другом с помощью программируемых трассировачных линий, как показано на рисунке ниже.

Идеей, реализованной в FPGA, является прямое задание логических функций в виде таблицы истинности (LUT, Look-Up Table). Вместо коммутации вентилей ИЛИ и И таблица истинности представляет собой просто блок памяти, на адресные входы которого подаются входные логические сигналы. Их комбинация естественным образом выбирает одну из ячеек таблицы, в которой хранится требуемое состояние ячейки – 0 или 1. Таким образом, LUT в FPGA может реализовать любую логическую функцию, если число её входов не превышает число входов LUT. Долгое время LUT в FPGA имели 4 входа, т.е. содержали 16 однобитовых ячеек памяти. Комбинация "4-входовый логический генератор и триггер" получила название "эквивалентная логическая ячейка" (equivalent logic cell) и часто используется для определения сложности схемы, хотя современные FPGA используют уже 6-входовые LUT.

Несколько логических ячеек объединяются в конфигурируемые логические блоки (КЛБ, Configurable Logic Block, CLB). Между блоками КЛБ, размещёнными на кристалле в виде прямоугольной матрицы, проложены программируемые трассировочные линии, а по периметру микросхемы располагаются программируемые блоки ввода-выводв (БВВ).

Соединение КЛБ трассировочными линиями также может регулироваться. На пересечении вертикальных и горизонтальных линий расположены программируемые трассировочные матрицы (Programmable Routing Matrix), которые так же, как LUT, управляются конфигурационной памятью FPGA. В современных FPGA присутствует достаточное число трассироваочных линий разных типов (от локальных, соединяющих соседние КЛБ, до глобальных, пересекающих весь кристалл или его крупный регион). Как правило, числа трассировочных линий достаточно для выполнения всех соединений проекта, однако при высокой степени использования КЛБ и слишком сложных соединениях число трассировочных линий может оказаться недостаточным. Поэтому от FPGA не стоит ожидать 100%-го использования программируемых ячеек.

Реализацию цифровой схемы в FPGA можно проиллюстрировать следующим образом:

В логические ячейки КЛБ заносятся требуемые таблицы истинности, при необходимости подключаются триггеры логических ячеек. Соединения с другими ячейками выполняются с помощью замыкания соответствующих коммутационных транзисторов в трассировочных линиях.

На рисунке видно, что две ячейки из всего массива оказались запрограммированы на реализацию определённой логической функции. Поскольку для реализации схемы одной ячейки оказалось недостаточно, её выход был подключён к входу другой ячейки, для чего задействованы трассировочные линии FPGA. Чтобы реализовать такую схему, необходимо задать режимы работы отдельных компонентов внутри ячеек, а также активировать цифровые ключи, соединяющие отдельные сегменты трассировочных линий. Настройки компонентов и информация о включенных/выключенных коммутаторах хранится в специальной памяти внутри FPGA. Поскольку эта память выполнена по технологии SRAM, она имеет неограниченное число циклов перезаписи, однако теряет информации при пропадании питания. Поэтому интерфейс программирования и внешняя энергозависимая микросхема являются обязательными для работы с FPGA.

На практике программирование ячеек и формирование трассировочных линий выполняется автоматически с помощью системы автоматизированного проектирования. Структура файла конфигурации является строго конфиденциальной информацией, и формирование такого файла может быть выполнено только с помощью САПР конкретного производителя FPGA.

Основные особенности подхода, реализованного в FPGA:

- FPGA подразумевают гранулярность схемы, это значит, что сложные с не равномерным использованием компонентов всё равно необходимо приводить к базовым возможностям логических ячеек, причём вероятнее всего какие-то возможности ячеек будут незадействованы;

- программируемые трассировачные линии имеют большую задержку распространения сигнала по сравнению с металлическими соединителями интегральных схем, поэтому рабочие частоты ПЛИС оказываются меньше, чем частоты заказных/полузаказных СБИС.

Таким образом, проекты на базе ПЛИС оказываются медленнее и дороже решения на базе стандартных (Standart Product) или специализированных микросхем (ASIC, ASSP – Application-Specific Integrated Circuit, Application-Specific Standart Product). Но поскольку стоимость подготовки производства интегральных схем постоянно растёт и, например, для технологического процесса с нормой 32 нм достигала 200 млн. долларов США (по данным на 2012г), то разработка специализированной микросхемы оказывается экономически целесообразной только для массового производства. А для устройств, выпускаемых небольшими тиражами ПЛИС являются подходящей элементной базой.

Слайд: FPGA фирмы Xilinx

Одним из основных производителей ПЛИС является фирма Xilinx. В конце 90х годов основной линейкой FPGA среди продукции Xilinx была серия XC4000 (семейства XC4000E, XC4000XL и XC4000XLA). Архитектура этой линейки оказалась довольно удачной, однако выяснилось, что в целом ряде проектов возможности стандартной ячейки ПЛИС используются далеко не полностью. Возникла естественная альтернатива – использовать дорогие устройства с максимальной производительностью и полным набором функциональных возможностей или, напротив, дешевые ПЛИС, обеспечивающие базовые функции, требующиеся для большинства типовых проектов. В результате фирма Xilinx начала выпускать различные серии FPGA, отвечающие упомянутым альтернативам.

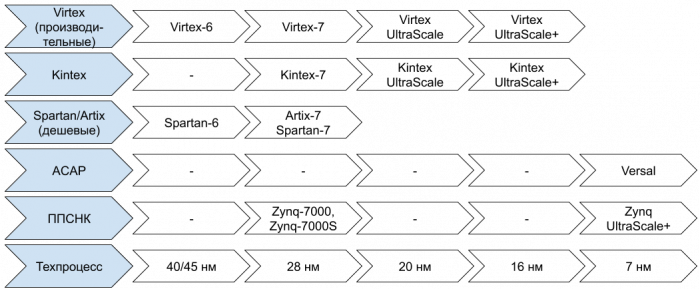

Стандартное недорогое решение представляла серия Spartan, на смену которой пришли серии Artix (минимальная стоимость) и Kintex (умеренная стоимость при высокой производительности в задачах цифровой обработки сигналов), наилучшие технические характеристики достигаются в серии Virtex. На данный момент активными являются семейства серии 7 – Artix-7, Spartan-7, Kintex-7, Virtex-7. Микросхемы UltraScale и UltraScale+ относятся к верхнему ценовому диапазону и предназначены для построения сложных систем с максимальной степенью интеграции компонентов на кристалле. Ячейки серии Kintex ничем не отличаюися от ячеек более дорогой серии Virtex.

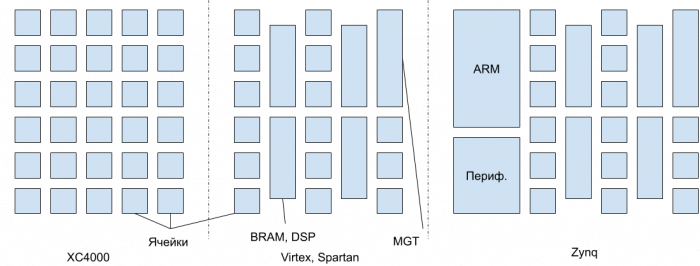

Слайд:Архитектура FPGA фирмы Xilinx

Архитектура ранних семейств (например, XC4000) представляла собой прямоугольную сатрицу однотипных логических ячеек, окруженных блоками ввода-вывода. Такая архитектура выглядит однородно и в целом удобна для реализации самых разных цифровых схем. Однако с учётом сниженной тактовой частоты программируемой схемы и необходимостью тратить существенную часть площади кристалла на коммутационные линии и неиспользуемые ресурсы ячеек, выяснилось, что целый ряд широко используемых компонентов реализуется в FPGA крайне неэффективно.

Поэтому в начале 2000-х годов FPGA Xilinx кроме собственно логических ячеек содержали уже аппаратные блоки. В первую очередь были добавлены:

- блоки синхронной статической двухпортовой памяти (Block RAM, BRAM). В более современных семействах были добавлены также и более крупные блоки памяти UltaRAM;

- умножители независимых целочисленных операндов, позже превратившиеся в "блоки цифровой обработки сигналов", реализующие операцию "умножение с накоплением", обозначаемые как XtreameDSP или DSP48;

- высокоскоростные последовательные приемопередатчики (MultiGigabit Transceivers, MGT).

Отдельным направлением ПЛИС, анонс которого состоялся в 2011 году, являются микросхемы класса All Programmable SoC (ППСНК, полностью программируемые системы на кристалле). Первыми из микросхем такого типа являются AP SoC семейства Zynq-7000. Они включают в себя процессорное ядро ARM и матрицу программируемых логических ячеек, аналогичных применяемым в Artix или Kintex. Zynq-7000 имеют также разновидность Zynq-7000S, отличающуюся одноядерной, ане двухядерной подсистемой ARM.

Семейство UltaScale+ также включают микросхемы Zynq. ОНи обозначаются Zynq UltraScale+ и имеют несколько разновидностей.

Новым направлением архитектуры ПЛИС является анонсированная в 2018 году Adaptive Compute Acceleration Platform (ACAP), или адаптивная платформа ускорения вычислений. В настоящее время она представлена серией Versal, первые образцы которой выпускаются по технологическому процессу с нормами 7 нм. ПЛИС Versal объединяют матрицу программируемых ячеек, аппаратные процессоры ARM и сеть аппаратно реализованных 32-разрядных RISC-процессоров.

В настоящее время сохраняют некоторую актуальность недорогие ПЛИС Spartan-6, однако основной интерес представляет серия 7, представленная наибольшим числом разновидностей семейств.

Ниже диаграмма соответствия поколений ПЛИС Xilinx технолгическим процессам.

Слайд:Аппаратный состав FPGA фирмы Xilinx

Итак, кроме логических ячеек и блоков вводв-выводв современные FPGA содержат большое число аппаратных блоков, реализующих часто используемые в цифровой схемотехнике функции. Смысл размещения на кристалле таких блоков состоит в том, что те же узлы, выполняемые с помощью логических ячеек, будут именть больший размер и пониженное быстродействие. В то же время аппаратная реализация часто используемых блоков несущественно увеличивает площадь кристалла и стоимость.

К аппаратным блокам размещённым в FPGA относятся:

- блоки синхронной статической двухпортовой памяти BRAM;

- блоки цифровой обработки сигналов "умножение с накоплением" Xtreme DSP;

- формирователи тактовых сигналов MMCM (Multi-Mode Clock Managers) и PLL (Phase-Locked Loop);

- скоростные последовательные приемопередатчики (MGT, Multi-Gigabit Transceivers);

- контроллеры PCI Express endpoint и root;

- процессорные ядра ARM (Zynq-700, Zynq-7000S, Zynq-US+).

Семейство Spartan-6 выполнено по нормам 45-нм. В состав семейства входят несколько микросхем в диапазоне логической ёмкости от 4 до 150 тысяч эквивалентных логических ячеек. Стоит отметить, что характеристики и сферы применения FPGA всё больше ориентируются на аппаратные ядра в этих микросхемах. Для семейств Spartan это блочная память и секции DSP. Они способны работать на высокой тактовой частоте (275...325 МГц в зависимости от класса скорости ПЛИС) и потребляют не больше энергии, чем аналогичные устройства в микроконтроллерах.

Важным преимуществом ПЛИС является возможность организовывать специальные вычислительные блоки построенные на базе секций DSP. Такие блоки могут работать полностью параллельно и обеспечивать суммарную производительность, превосходящую производительность не только микроконтроллеров, но и сигнальных процессоров. Например, 16 секци DSP, работающие на частоте 200 МГц (это вполне достижимо для многих модулей ЦОС), дают суммарную производительность, эквивалентную гипотетическому процессору с тактовой частотой 3,2 ГГц.

ПЛИС обладает существенно меньшим разнообразием накристалльных периферийных устройств. Такие компоненты, как флеш-память или EEPROM, АЦП, ЦАП, USB, должны быть реализованы во внешних микросхемах.

В таблице ниже показаны сравнительные характеристики семейств начального уровня.

| Характеристика | Spartan-6 | Spartan-7 | Artix-7 | Zynq-7000 |

|---|---|---|---|---|

| Логические ячейки, тыс. | 4-150 | 6-100 | 12-215 | 23-85 |

| Блочная память, Мбит | 0,2-4,8 | 0,18-4,3 | 0,72-13,1 | 1,8-4,9 |

| Секции DSP | 8-180 | 10-160 | 40-740 | 60-220 |

| Приемопередатчики | 0-8 | - | 2-16 | 0-16 |

| Максимальная скорость приемопередатчиков, Гбит/с | 3,2 | - | 6,6 | 6,6 |

| Число программируемых внешних выводов, максимум | 576 | 400 | 500 | 328 |

Слайд:Логические ячейки FPGA

Логические ячейки являются основным программируемым ресурсом FPGA, определяющим её архитектуру как таковую и наиболее универсальным с точки зрения функциональных возможностей.

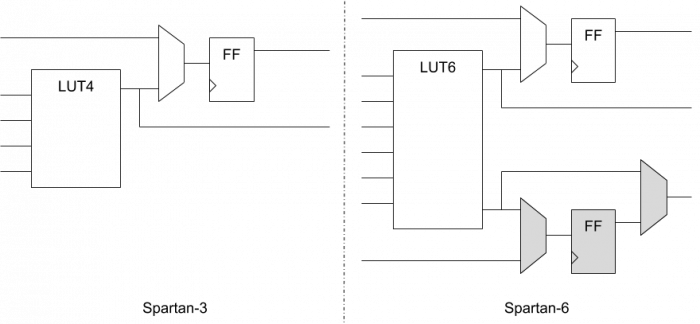

В современных семействах, включая Spartan-6, серию 7 и последующие, ячейка состоит из 6-входовой таблицы истинности (LUT, Look-Up Table) и двух триггеров.

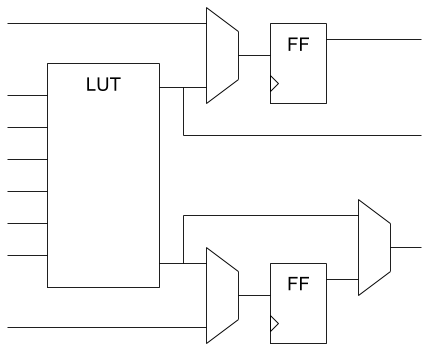

На протяжении развития FPGA архитектура логической ячейки претерпевала изменения, которые схематично можно проиллюстрировать следующим образом:

Можно увидеть, что от 4-х входовой LUT ячейки перешли 6-и входовой и от одного триггера в ячейке к двум.

Слайд:Комбинационная логика на базе LUT

Комбинационная логика реализуется в таких ячейках путём заполнения таблиц истинности, представляющих собой модули памяти. Комбинация состояний на входах для такого модуля является адресом ячейки, хранящей ребуемое значение выхода. Такой подход позволяет реализовать произвольную логическую функцию, поскольку независимо от сложности схемы все возможные состояния выхода записываются в память. Эта память представляет собой ОЗУ, и её содержимое записывается в процессе загрузки конфигурации FPGA.

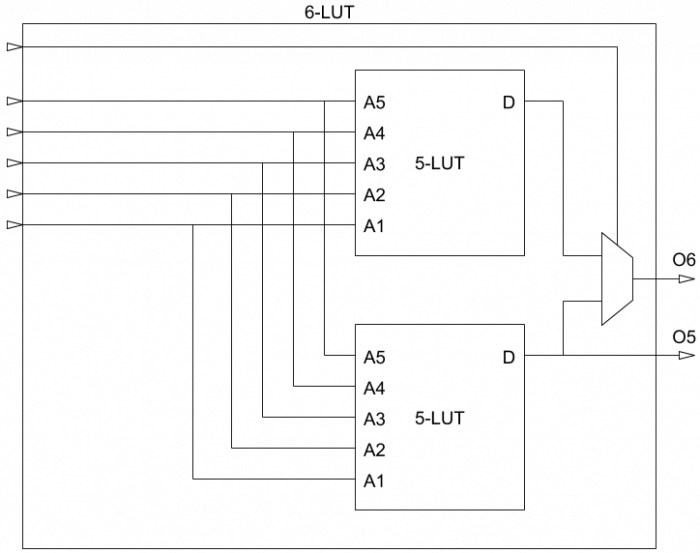

LUT реализует любую функцию с не более чем 6 операндами. Кроме того, возможно использование LUT в режимес частично совмещёнными входами, когда память разбивается на два фрагмента по 21 бита, давая возможность сформировать две логические функции с не более чем 5 операндами каждая. При этом, поскольку в самой LUT всехо 6 входов, часть входов должна быть обобщена. Такой режим используется САПР по мере возможности.

Слайд:LUT в режиме распределенной памяти (distributed memory)

LUT могут также использоваться в режимах распределенной памяти (distributed memory) и сдвиговых регистров. Поскольку логический генератор представляет собой элемент статической памяти, который хранит таблицу истинности в явном виде, его можно использовать по прямому назначению – в качестве обычного компонента памяти.

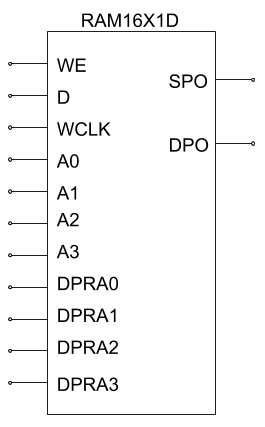

Распределённая память может работать в однопортовом или простом двухпортовом (Simple dual-port) режимах. Простой двухпортовый режим имеет ограничение, что только один порт может использоваться для чтения и записи, а второй предназначен только для чтения. На рисунке ниже элемент распределённой памяти, который имеет следующие сигналы:

- we – сигнал разрешения записи;

- d – данные для записи

- wclk – вход тактового сигнала;

- a – адрес для чтения/записи;

- dpra – адрес для чтения, второй порт (dual port read address);

- spo – выход первого порта (single port output);

- dpo – выход второго порта (dual port output).

Распределённая память удобна для организации небольших блоков данных – буферов, линий задержки, небольших таблиц. Реализация больших блоков на распределённой памяти в общем случае нецелесообразна из-за сильной фрагментации такого блока. Для объёмов в 512 слов и больше удобнее использовать блочную память.

Тем не менее распределённая память обладает важным свойством, отсутсвующим у блочной памяти, – она допускает асинхронное чтение.

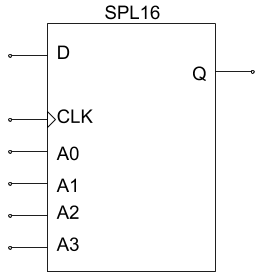

Слайд:Сдвиговый регистр на базе LUT

Другой вариант использования логического генератога – реализация на его базе сдвигового регистра. Ниже представленно графическое обозначение такого компонента, который имеет следующие сигналы:

- D – данные для записи в сдвиговый регистр;

- CLK – тактовый сигнал;

- A – адресный вход;

- Q – выход данных.

В простейшем варианте сдвиговый регистр может представлять собой модуль, задерживающий входной сигнал на N тактов.

LUT в режиме сдвигового регистра может использоваться совместно с триггером той же логической ячейки, увеличивая глубину сдвигового регистра на 1.

Слайд:Триггер в логической ячейке

Один из вариантов графического изображения триггера представленно ниже:

Где триггер может иметь следующие сигналы:

- C – вход тактового сигнала;

- D – вход данных;

- CE – вход разрешения записи (clocl enable);

- CLR – вход ассинхронного сброса (clear);

- PRE – вход ассинхронной установки в логическую единицу (pre-set);

- R – вход синхронного сброса (reset);

- S – вход синхронной установки в логическую единицу (set);

- Q – выход данных.

Физически существует только по одному сигналу сброса/установки S/R. Сброс, установка (синхронные или ассинхронные) реализуются путём комбинирования триггера с другими ресурсами ячейки.

Слайд:Секция (slice) в FPGA

Логические ячейки входят в состав секции (slice), которая объединяет 4 логические ячейки. Понятие секции введено потому, что кроме LUT и триггеров она имеет дополнительные компоненты.

Дополнительные компоненты секции – это цепи ускоренного переноса и мультиплексоры. Цепи ускоренного переноса служат для построения сумматоров и вычитателей. Поскольку операции сложения и вычитания широко используются в цифровой схемотехнике, для них в ячейку были добавлены специальные компоненты, которые вычисляют сумму и передают бит переноса на следующий аналогичный компонент соседней секции. Синтезаторы автоматически поддерживают такие конструкции, поэтому выражения вида a + b будут реализованы с использованием цепей ускорения переноса. Не следует пытаться описывать сумматоры с помощью эквивалентных логических выражений, поскольку в этом случае они будут реализованы в виде таблиц истинности в LUT, а не на базе специализированных цепей.

Дополнительные мультиплексоры F7MUX объединяют выходы двух LUT. Эти блоки могут быть полезны в ряде случаев, уменьшая число LUT, требуемых для построения логического узла. Например, схема с 7 входами может быть реализована не на двух LUT, а на связке LUT + F7MUX. Такие преобразования автоматически выполняются синтезатором и обычно не требуют мпециального внимания разработчика.

Слайд:Конфигурируемый логический блок (Configurable Logic Block) в FPGA

Две секции образуют конфигурируемы логический блок (КЛБ, CLB – Configurable Logic Block). Рассматривать КЛБ можно начать с семейства Spartan-6, поскольку в нём появилось заметное нововведение в виде трёх разновидностей логической ячейки. Полезной осбенностью FPGA Xilinx традиционно являлась возсожность использования LUT в режимах распределённой памяти 1x16 или свдигового регистра. Впоследствии число таких универсальных ячеек было сокращено, и появились секции SliceM и SliceL (символы M и L обозначают Memory и Logic соответсвенно, т.е. ряд ячеек мог реализовывать функцию памяти, а остальные – только логику). Вместе с тем оба типа секций располагались в рамках каждого КЛБ, т.е. оба типа секций распределялись равномерно по всей матрице КЛБ. В Spartan-6 появился третий тип – SliceX. Это менее мощная разновидность секции, поскольку в ней отсутствует цепь ускоренного переноса, т.е. такая секция не может служить для организации сложения или вычитания.

В итоге в КЛБ Spartan-6 оказываются следующие секции:

- SliceM – универсальная секция с LUT, конфигурируемым во всех режимах, а также с линиями ускоренного переноса;

- SliceL – LUT конфигурируется только как логический генератор, есть цепи ускоренного переноса;

- SliceX – LUT конфигурируется только как логический генератор, нет цепей ускоренного переноса.

Их двух КЛБ один содержит пару секций SliceL+SliceX, а другой – SliceM+SliceX. Такие КЛБ называются CLB_LX и CLB_MX соответсвенн.

Для эффективного использования ресурсов логических ячеек и секций следует обращать внимание на возможность реализации сложения/вычитания с помощью цепей ускоренного переноса, а мультплексоров – с применением дополнительных мультиплексоров секций. Для этого операции сложения/вычитания и мультиплексирование (например, с помощью конструкций switch или case в VHDL) рекомендуется использовать по мере возможностей.

Слайд:Отличия секций серии 7 и UltaScale от секций Spartan-6

В серии 7 используется комбинация из одной секции SliceM и трёх секций SliceL. Секции SliceX Не используются, таким образом, все секции имеют цепи ускоренного переноса.

Кроме мультиплексоров F7MUX, объединяющих выходы двух LUT, в секциях серии 7 есть мультиплексоры F8MUX, объединяющие выходы двух F7MUX. Таким образом, некоторые варианты схем могут быть реализованы с использованием меньшего числа секций в ПЛИС серии 7 по сравнению с Spartan-6.

В семействе UltaScale, следующим за серией 7, выходы мультиплексоров F8MUX объединяются мультиплексором F9MUX. Все мультиплексоры применяются синтезатором автоматически, без явного участия разработчика.

Можно выделить основные компоненты секции:

- таблицы истинности (4 шт.);

- триггеры (8 шт.);

- мультиплексоры F7MUX и F8MUX;

- цепь ускоренного переноса.

Слайд:Блоки ввода вывода в FPGA

Блоки ввода-вывода связвывают FPGA с внешними устройствами. Они представляют собой двунаправленные цифровые выводы, которые могут программироваться как по направлению (вход, выход, выход с третьим состоянием, двунаправленный вывод), так и по типу электрического интерфейса (ТТЛ, КМОП, LVDS и т.д., всего более 40 типов интерфейсов, включая дифференциальные). Блоки могут попарно объединяться для реализации дифференциальных интерфейсов (например, LVDS). Необходимо учитывать, что выводы не могут образовывать пары в произвольном порядке – каждая пара строго фиксирована в корпусе ПЛИС.

ВСТАВИТЬ РИСУНОК

На рисунке выше символы P и N обозначают непосредственно контактные площадки, подключенные к выводам корпуса ПЛИС.

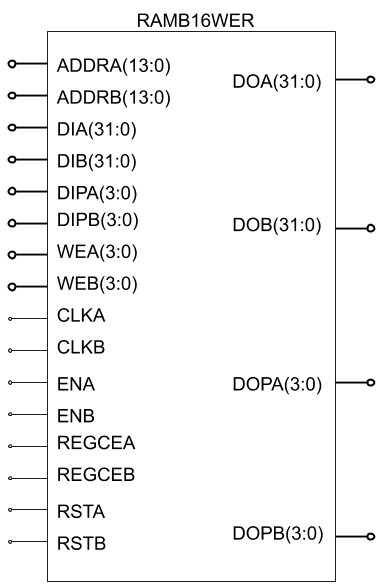

Слайд:Блочная память в FPGA

Блочная память является показательным примером встроенного аппаратного ресурса, повышающего эффективность ПЛИС при решении типовых задач схемотехники. Блок памяти занимает гораздо меньше места, чем аналогичный по ёмкости блок, выполненный на распределённой памяти логических ячеек, и к тому же обладает высокими характеристиками производительности. Память является "истинно двухпортовой" (true dual port). Это означает, что она имеет два независимых набора сигналов, допускающих проведение операций чтения или записи одновременно. Альтернативой является разновидность simple dual-port, когда только один порт допускает и чтение, и запись, а второй работает в режиме "только чтение".

Память в Spartan-6 размещается блоками по 18 кбит. Графическое представление компонента блочной памяти показано ниже, где сигналы имеют следующие обозначения (сигналы с именами заканчивающимися на A и B соответсвуют портам A и B):

- ADDRA, ADDRB – входы адреса;

- DIA, DIB – входы данных для записи;

- DIPA, DIPB – дополнительные разряды двходов данных;

- WEA, WEB – входы разрешения записи;

- CLKA, CLKB – тактовые сигналы;

- ENA, ENB – сигналы разрешения работы;

- REGCA, REGCB – разрешение записи во внутренний конвейеризирующий регистр данных;

- RSTA, RSTB – входы сброса внутренних регистров данных (сброс массива ячеек памяти с помощью этих сигналов невозможен);

- DOA, DOB – выходы данных;

- DOPA, DOPB – дополнительные разряды выходов данных.

Память, несмотря на физическую организацию в виде массива 1024 X 18 бит, может выступать в различных конфигурациях: 16k X 1, 8k x 2, 4k x 4, 2k x 9, 1k x 18, 512 x 36. Разработчик сожет самостоятельно контролировать используемый режим или использовать результаты синтеза.

Память BRAM может быть автоматически сгенерирована синтезатором на основе анализа исходных текстов проекта. Разработчик может принудительно задать использование такой памяти в проекте, установив подключение сигналов (component instantiation).

При одновременном доступе к ячейке памяти по двум портам, когда один из портов производит запись, а другой – чтение, возможны следующие режимы работы:

- чтение перед записью (read before write) – порт, выполняющий чтение, выдаёт старое значение ячейки памяти, в которую производится запись по другому порту;

- чтение после записи (read after write) – порт, выполняющий чтение, выдаёт значение, которое записывается по другому порту;

- нет чтения при записи (no read on write), состояние порта не изменяется.

В последнем случае речь идёт не об отстуствии записи в ячейку, а о сохранении состояния выходного регистра модуля памяти.

Слайд:Секции DSP48 в FPGA

Слайд:Тактовые ресурсы FPGA

Для повышения надежности работы проектов на базе FPGA применяемвые схемы должны быть синхронными, поскольку большинство приёмов, основанных на ассинхронной схемотехнике хотя и реализуемы технически для FPGA, однако часто приводят к нестабильной работе. Это связано с тем, что уменьшение технологических норм и повышение тактовых частот делают цифровые схемы крайне чувствительными к особенностям трассировки, технологическому разбросу параметров, температуре и колебаниям напряжения питания.

Основные параметры тактового сигнала:

- период;

- jitter ("дрожание");

- skew (время нарастания фронта).

ВСТАВИТЬ РИСУНОК

Время нарастания фронта обычно измеряется от уровня 10% максимального напряжения до 90% (в некоторых случаях – 20% ... 80%). Это связано с тем, что непосредственно вблизи нуля и максимального напряжения форма сигнала обычна искажена и на практике точного нуля и максимума фронт может и не достигать. В то же время параметр skew важен тем, что срабатывание может произойти при различных уровнях напряжения по мере прихода фронта. Возможна ситуация, когда один триггер воспримет фронт в положении ближе к максимуму, а следующий за ним – на начальном участке. В этом случае вместо номинального значения периода интервал между срабатываниями последовательно включенных триггеров будет меньше на величину времени нарастания сигнала.

Понятие jitter соответствует эффекту "дрожания" фронта относительно его номинального положения на временной оси. Это связано с нестабильностью частоты тактового генератора. Так же, как и для параметра skew, возможно ситуация, когда первый триггер сработает по положению фронта, пришедшего с максимальной задержкой, а следующий фронт придёт с минимальной задержкой. В этом случае интервал времени для распространения сигнала по линии данных должен быть уменьшен ещё и на величину jitter.

Из-за наличия упомянутых эффектов тактовый сигнал желательно иметь с минимально возможными значениями параметров skew и jitter. Поэтому необходимо применять специальные формирователи (буферные элементы), обеспечивающие минимальное значение skew, и генераторы, минимизирующие jitter. Такие компоненты имеются на кристаллах современных ПЛИС.

Все синхронные компоненты (триггеры, блочная память, блоки DSP) получают тактовый сигнал по выделенным линиям, который проложены по кристаллу так, чтобы минимизировать неравномерность распространения сигнала. Если использовать именно эти ресурсы, то можно считать, что все синхронные компоненты работают одновременно. В противном случае возможно возникновение так называемых "гонок фронтов", когда фронт тактового сигнала приходит на отдельные компоненты в разные моменты времени и в кристалле будут одновременно существовать данные, относящиеся к разным отсчётам тактового сигнала. Комбинация сигналов, относящихся к разным тактам, скорее всего приведёт к неправильному поведению схемы. Нельзя сказать, что такие ситуация происходят всегда, однако следует уделить внимание этому вопросы при проектировании.

В ПЛИС Spartan-6 предусмотрены специальные буферы для распространения тактового сигнала, однако они расположены только в определённых блоках ввода/вывода, которые помечены в документации.

Слайд:Высокоскоростные последовательные приемопередатчики FPGA

Слайд:Аппаратные контроллеры PCI Express

Слайд:Модуль DeviceDNA

Слайд:Модуль AMS (Agile Mixed Signal, только для серии 7)

TODO:

- Какие основные поставщики?

- Структура CPLD фирмы XILINX