Ata5577/Спецификация микросхемы Ata5577

- Спецификация программы

- Спецификация на считыватель

- Спецификация ИМС Ata5577

- Тестовый план

- Цифровой блок

Спецификация

Характеристики

- бесконтактное питание;

- бесконтактное чтение/запись при передаче данных

- частота FRF от 100 кГц до 150 кГц

- Два режима работы: основной и расширенный

- совместима с Atmel® T5557, ATA5567

- замена для Atmel e5551/T5551 в наиболее распространенных режимах работы

- настраиваемая для совместимости с ISO/IEC 11784/785

- память ЭСППЗУ (EEPROM) содержит 363-бит: 11 блоков (32 бита + один бит блокировки)

- 7 × 32 бит EEPROM памяти пользователя, включая 32-бита для хранения пароля

- 2 × 32 бит для уникального ID

- 1 × 32-разрядный регистр настроек (option register) в EEPROM для настройки аналогового интерфейса (Analog Front End = AFE):

- уровень детектирования тактового сигнала и паузы (gap)

- улучшенная синхронизация передачи данных в карту (Improved downlink timing)

- фиксация и напряжение модуляции (Clamp and modulation voltage)

- мягкое переключение модуляции

- затухание в командах записи, как это реализовано в Atmel T5557/ATA5567 или с помощью резистора

- загрузка данных протокола (Downlink protocol)

- 1 × 32-разрядный регистр конфигурации (configuration register) в EEPROM для того, чтобы установить:

- скорость передачи данных:

- от RF/2 до RF/128, согласно бинарному делению (binary selectable) или

- фиксированная скорость базового режима (Fixed Basic Mode rate)

- модуляция/кодирование:

- би-фазная, манчестерский код, FSK, PSK, NRZ

- другие опции:

- режим с паролем

- функция задания числа блоков для чтения (Max block feature)

- режим прямого доступа (чтение блока)

- последовательность терминатора(?) (Sequence terminator(s))

- защита записи каждого блока (с помощью бита блокировки)

- режим ответа по запросу (AOR - Answer-On-Request)

- инвертирование выходных данных

- отключение доступа тестового режима (Disable test mode access)

- быстрая загрузка данных на карту (~6 кбит/с вместо ~3 кбит/с)

- ОТР функциональность (однократная запись)

- начальная задержка (~67 мс)

- скорость передачи данных:

Описание

The Atmel® ATA5577C это безконтактная интегральная схема чтения/записи для применения на частотах от 125kHz до 134kHz. Одна катушка, соединенная с чипом, служит как источник питания инегральной схемы, также как двунаправленный интерфейс связи. Антенна и чип вместе формируют передатчик. 363-bit память EEPROM на чипе (11 блоков по 33 бита каждый) может быть прочитана и записана поблоково базовой станцией (считывателем). Данные передаются от IDIC (выгрузка данных) с помощью загрузочной модуляции. Это достигается затуханием радиочастотного поля резистивной нагрузкой между двумя терминалами (клеммами), катушкой 1 и катушкой 2. Интегральная схема получает и декодировует сериализованные команды базовой станции (загрузка данных в карту), которые зашифрованы как модулированные на 100 процентов амплитуды, закодированные импульсными интервалами потоки битов.

Совместимость

The Atmel ATA5577C спроектирован таким образом, чтобы быть совместимым с Atmel T5557/ATA5567. Структура регистра настроек у них идентична. Два режима, базовый и расширенный, также доступны. Atmel ATA5577C в состоянии заменить Atmel e5551/T5551 во всех самых распространенных режимах работы. Во всех применениях, корректное функционирование замены должно быть оценено и подтверждено. Для дальнейших деталей смотрите веб-сайт Atmel.

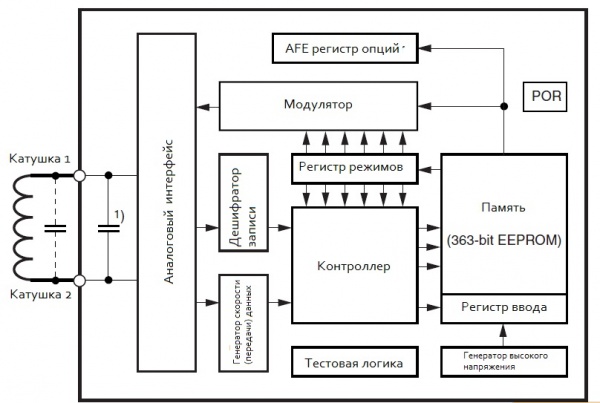

Диаграмма системного блока

Функциональные блоки блоки

Аналоговый интерфейс (Analog Front End – AFE)

Аналоговый интерфейс включает все схемы, которые напрямую соединены с терминалами катушек. Он генерирует питание интегральной схемы и управляет двунаправленной передачей данных с/на считыватель. Он состоит из следующих блоков:

- Выпрямитель, который генерирует постоянное напряжение питания из переменного напряжения катушек*

- Извлечение clock-сигнала*

- переключаемая нагрузка между катушкой 1 и катушйок 2 для передачи данных от передатчика к считывателю*

- Детектор полевых интервалов для передачи данных от базовой станции к передатчику*

- Схемы защиты ESD*

АFE регистр опций (AFE Option Register)

Регистр опций поддерживает читаемую теневую копию данных, хранящихся в блоке 3, странице 1 EEPROM. Он содержит настройки уровня аналогового интерфейса и порогового уровня, а также расширенный выбор протоколов исходящих соединений, с помощью которого устройство может быть точно настроено для идеальной работы и любых применяемых сред. Он постоянно обновляется в режиме чтения и перезагружается после каждого сброса при включенном питании или команды сброса. По умолчанию, регистр опций пре-программирован согласно таблице 10-1.

Генератор скорости передачи данных

Скорость передачи данных программируется двоично, чтобы работать на любой целочисленной скорости между RF/2 и RF/128, или на одной из фиксированных скоростей базового режима (RF/8, RF/16, RF/32, RF/40, RF/50, RF/64, RF/100 и RF/128).

Дешифратор записи

Дешифратор записи обнаруживает интервалы записи и проверяет правильность потока данных согласно протоколу загрузки данных Atmel e555x (кодировка с импульсными интервалами).

Генератор высокого напряжения

Эта схема накачки заряда генерирует высокое напряжения, требуемое для программирования EEPROM.

Питание постоянного тока

Питание подается на IDIC извне через два соединения катушек. IC корректирует и регулирует этот источник радиочастот и использует его для генерации своего напряжения питания.

Сброс по включению питания (POR — Power On Reset)

Схема сброса по включению питания блокирует подачу напряжения питания до тех пор, пока выпрямленное напряжение питания не достигнет приемлемого для работы уровня напряжения.

Извлечение тактового сигнала

Схема извлечение тактового сигнала(clock) использует внешний радиочастотный сигнал в качестве своего внутреннего источника тактового сигнала (clock).

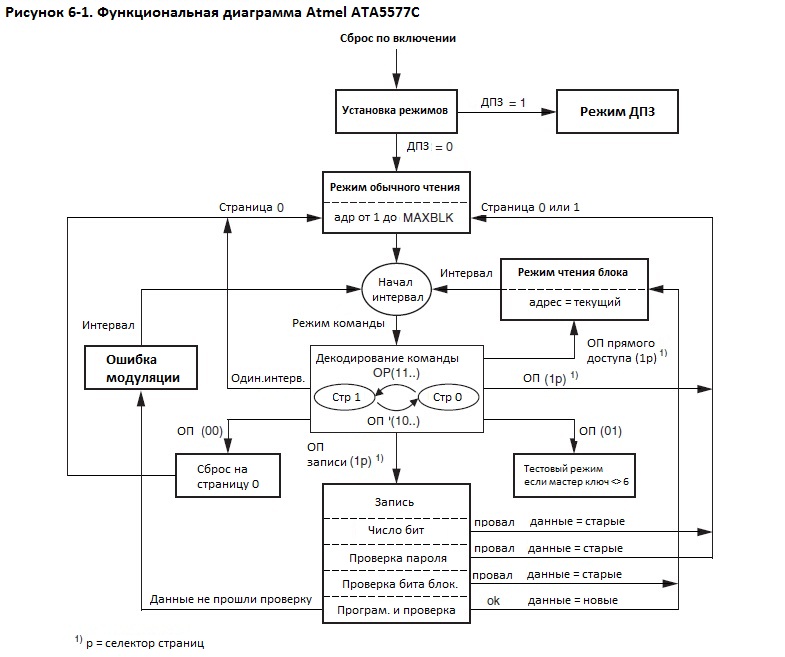

Контроллер

Модуль контроля логики выполняет следующие функции:

- Загружает в регистр режимов данные конфигурации из EEPROM (блок 0) после включения питания и во время записи

- Загружает в регистр опций настройками для аналогового интерфейса, хранящиеся в EEPROM странице 1 блоке 3 после включения и вовремя записи

- Управляет доступом на чтение/запись памяти EEPROM и защитой данных

- Выполняет декодирование команды входного соединения, определяет нарушение протокола и ошибочные условия

Регистр режима

Регистр режима содержит доступную для чтения теневую копию данных конфигурации, которые хранятся в блоке 0 EEPROM. Он постоянно обновляется в режиме чтения и перезагружается после каждого сброса при включенном питании или команде сброса. Изначально регистр режимов пре-программирован с значениями TBD

Модулятор

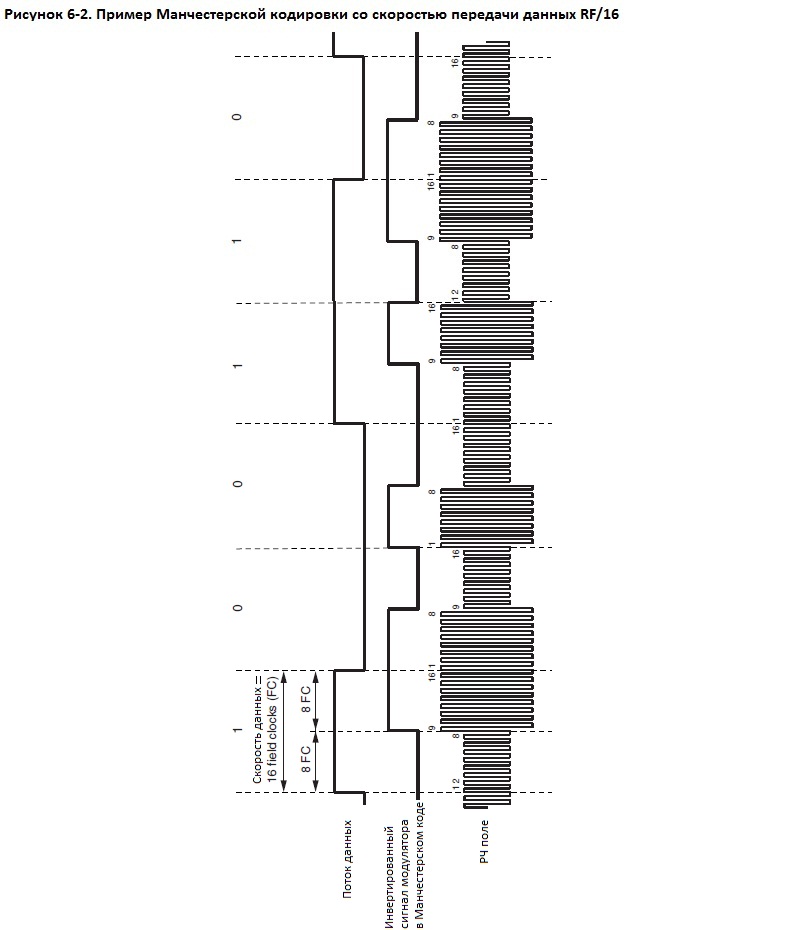

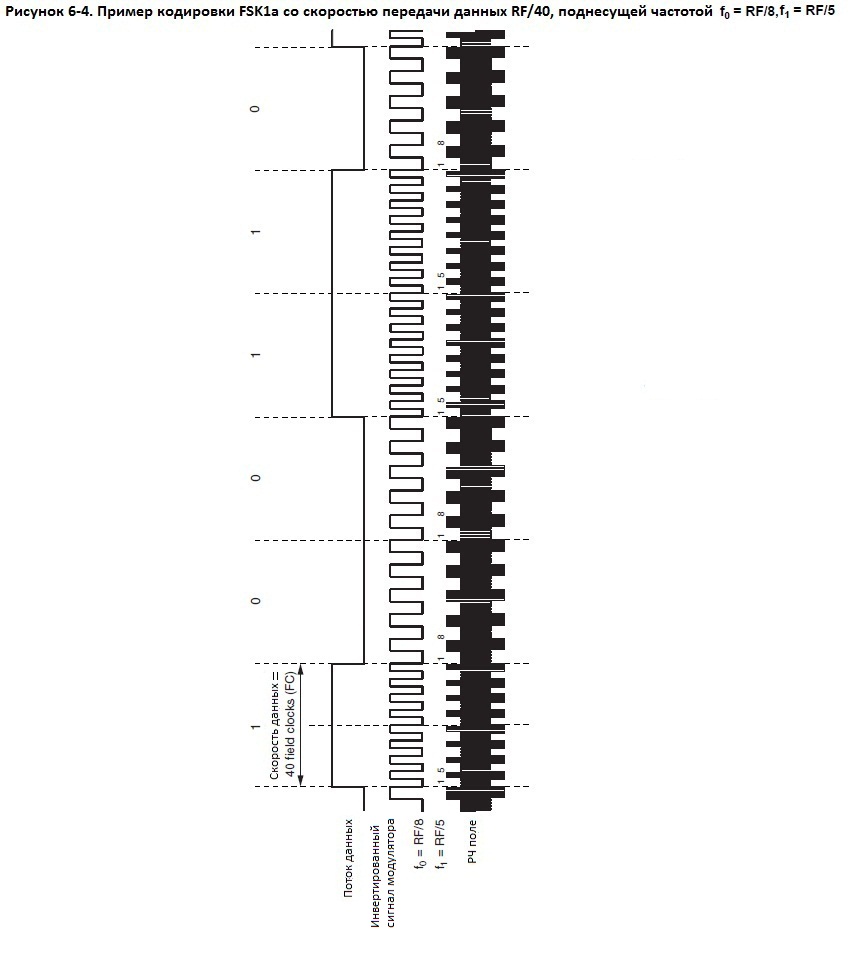

Модулятор шифрует сериализованные данные (памяти) EEPROM для передачи их устройству чтения (карт) или базовой станции. Дотсупно несколько типов модуляции, например: Manchester, bi-phase, FSK, PSK and NRZ.

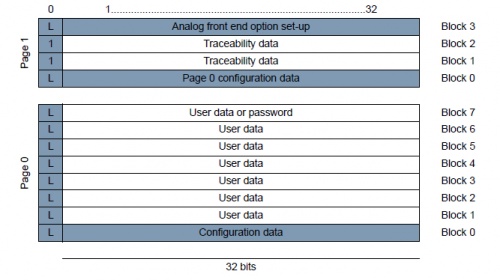

4.12 Память микросхемы

- Память содержит 363-бит EEPROM, которые расположены в 11 блоках из 33 бит каждый.

- Каждый блок включает в себя один бит блокировки, которая отвечает за защиту от записи соответствующего блока. (0 - разрешена запить???)

- Программирование осуществляется по-блочно, поэтому весь блок (в том числе и бит блокировки) может быть запрограммирован с помощью одной команды.

- Память разделена на две страницы.

- Страница 0 содержит 8 (восемь) блоков.

- Блок 0 Страницы 0 содержит данные конфигурации, которые не передаются во время регулярной операции чтения.

- Обращаясь к Блоку 0 всегда обращение будет происходить к Блоку 0 Страниц 0 независимо от того какая страница выбрана. Т.е. физически существует только один блок 0 и он используется для каждой страницы как нулевой блок.

- Блок 7 Страницы 0, может использоваться для хранения пароля защиты.

- Страница 1 состоит из 3 (трех) блоков. Все 33 бита блока, в том числе бит блокировки, программируются одновременно.

- Блок 3 Страницы 1 содержит данные конфигурации блока AFE (Analog Front End - аналоговый блок). Данные этого блока также не передаются во время операции чтения данных.

- Бит 0 каждого блока - бит блокировки для этого блока.

- После установки (в 0 или 1??) этого бита (в том числе блокировку немного?? себя) блок не программируется с помощью ВЧ-поля.

- Блоки 1 и 2 Страницы 1 содержат tranceability (трассируемые?) данные. Они передаются с параметрами (или как параметры), определенными в регистре Конфигурации (0 блок), только если приходит команда Opcode "11".

- Блоки tranceability данных программируются и заблокированы Atmel® (фирмой производителем)

Страница 1 Блок 1-2: Структура Traceability данных

- Блоки 1 и 2 страницы 1 содержат отслеживания данных и программируются и заблокированы Atmel ® во время производственных испытаний (1).

- Старший байт Блока 1 имеет значение E0h, обозначение класса (ACL). Как это определено в ISO / IEC 15963-1.

- Второй байт определен таким образом чтобы указывать на завод производителя, в соответствии с ISO / IEC 7816-6. Так как Atmel производитель то его ID 15H.

- Следующие 5 бит указывает чип ID (CID - "00001b"для Atmel ATA5577M1, и "00010" для Atmel ATA5577M2).

- Cледующие 3 бита содержат ревизию (версию микросхемы - ICR) (так использует Atmel - ICR = 010 для Atmel ATA5577C).

- Далее 40 бит данных, кодируют Traceability информацию фирмы Atmel, и соответствуют UID уникальному идентификационному номеру метки.

- Эти 40 бит данных содержат много ID (год, квартал, номер), номер пластины (Wafer#), число плохих пластин (DW).

Примечание: 1. Это действительно только для множества пластин поставляемых в фольге.

- Последние 40 бит могут содержать произвольный UID

Atmel Example

ACL Allocation class as defined in ISO/IEC 15963-1 = E0h

MFC Atmel Corporation manufacturer code as defined in ISO/IEC 7816-6 = 15h

CID 5 bit Chip ID for identification of the different products

“00001b” for Atmel ATA5577M1 and “00010b” for Atmel ATA5577M2

ICR 3-bit IC revision to identify foundry and/or revision of IC

Year 1-digit BCD encoded year of manufacturing

Quarter 2 bits for quarter of manufacturing

Number 14 bits of consecutive number

Wafer# 5 bits for wafer number

DW 15 bits designating sequential die number on wafer

5 Работа микросхемы

5.1 Настройка микросхемы

Примечания:

- Если поле option key = 6 (0110) или 9(1001), то опции AFE активированы. Для всех других значений, значение AFE принимают значения по умолчанию (все 0). Если вариант ключа 6 (0110), то "Cтраница 1" завершена (финализирована) (т. е. вариант регистра и traceability данных) не может быть перезаписана при любых попытках команды записи. Это означает, что если биты блокировки всех трех блоков "Cтраница 1" установлены и поле "option key" = 6, то все блоки Страницы 1 блокируются от изменений.

- Для работы в слабом поле.

Базовый режим

Расширенный режим

5.2 Мягкое (SOFT) переключение модуляции (5-7 бит AFE)

Резкий рост модуляции сигнала в начале модуляции – особенно в приложениях с высоким качеством антенны - может привести к потерям синхроимпульсов (тактовых сигналов) и, следовательно, нарушается временные интервалы. Чтобы предотвратить это, может быть выбрано несколько SOFT режимов модуляции для мягкого перехода при включении модулятора. (Soft) Мягкая модуляция должна использоваться только в комбинациях способа модуляции и скоростью передачи данных, которые не связаны с высокой частотой модуляции.

5.3 Демодуляция данных отсылаемых от метки к считывателю (19-20 биты AFE)

Мягкие (soft) модуляции приведут к дисбалансу в модулированных и немодулированных фазах. В зависимости от настройки мягкой модуляции, тактов в немодулированной фазе может быть больше, чем модулированной фазе. Чтобы сбалансировать это несоответствие, точки переключения от модулированных к немодулированным фазам может быть отложено на один или два импульса.

5.4 Затухание в командах записи (16-18 биты AFE)

Начало передачи команды от считывателя к метке инициализируется путем отправки Start GAP. Для облегчения обнаружения Start GAP относительно последующих пробелов (разрывов) между следующими данными, добавляется дополнительное затухание (нагрузка после первой паузы). Затухание активируется по умолчанию.

Данный подход особенно актуален при использовании антенн с высокой добротностью, более высокий коэффициент затухания может быть включен для улучшения времени разряда (затухания).

При использовании антенных катушек с низкой добротностью эта опция может быть отключена. Это приведет к повышению энергии во время приема команды, следовательно, улучшит расстояние записи.

5.5 Инициализация или стартовая задержка (32 бит)

- Схема сброса по включению питания (POR) остается включенной (выдает сигнал сброса) до допустимого порогового напряжения, после превышения рабочего напряжения сигнал сброса снимается. Это, в свою очередь, вызывает задержку инициализацию последовательности по умолчанию. В течении периода конфигурации это около 192 тактов, ATA5577C загружает данные во внутренний регистр инициализации со строк, хранящихся в Странице 0(1) Блоке 0 и параметров хранится в Странице 1 Блоке 3.

- Два варианта Atmel ATA5577C были реализованы (см. раздел 10. "Информация для заказа" на стр. 37).

- Вариант Atmel ATA5577C с затуханием во время инициализации, дает постоянное затухание во время инициализации (см. Рисунок 5-9 на стр. 19). Это предотвращает генерацию сброса при включении питания на границе рабочего расстояния. Это улучшает стабильность работы во всех приложениях, где максимальная дальность считывания не требуется.

- Вариант Atmel ATA5577C с типом без затухания помогает достичь большего диапазона чтения.

Тег начнет выдавать модуляцию в режиме регулярного (циклического) чтения спустя ~3 мс после ввода ВЧ-поля. Если бит задержки инициализации (32 бит) установлен, ATA5577C вариант с затуханием во время инициализации - то затухание остается постоянным на протяжении Т ~ 69мс на F = 125 кГц. ATA5577C вариант без затухания модуляция начнется после Т ~ 69мс.

- Init Delay = 0: Tinit = 192 × TC + TPOR = ~3 мс; где TC = 8 мкс при F = 125 кГц

- (TPOR означает задержку POR и зависит от условий окружающей среды)

- Init Delay = 1: Tinit = (192 + 8192) × TC + TPOR = ~69 мс

Любая пауза в поле, происходящая во время этого этапа инициализации будет перезапускать полную последовательность действий. Спустя времени инициализации, Atmel ATA5577C входит в регулярный режим чтения, и модуляция начинается автоматически в соответствии с параметрами, определенными в регистре конфигурации.

5.6 Модулятор Basic Mode (биты 16-20)

Модулятор может работать со следующими типами модуляции в основном режиме:

5.7 Максимальное число блоков (биты 25-27 )

После перехода в режим регулярного чтения, Atmel ATA5577C передает содержание данных, начиная с блока 1. Установка MAXBLK определяет, сколько блоков данных будут передаваться (0-7 значит 1 или 8 блоков).

5.8 Пароль (PWD: бит 28)

Когда поле активирования пароля активировано (PWD = 1), в команде, передаваемой от считывателя метке, первые 32 бита после кода операции OPCODE рассматриваются в качестве пароля. Они сравниваются по-битно с содержимым блока 7, начиная с бита 1. Если сравнение не удается, Atmel ATA5577C не будет переходить в режим программирования памяти. Вместо этого она перейдет в режим регулярного чтения после того как передача команды закончиться.

Примечание: В режиме пароля, MAXBLK должен быть установлен на значение ниже 7 для предотвращения передачи пароля от Atmel ATA5577C.

- Каждая передача команды прямого доступа (2 бита команды, 32-разрядный пароль, "0" бит, плюс 3 бита адреса = 38 бит) требует около 18 мс. Тестирование всех возможных комбинаций пароля (около 4,3 миллиарда комбинаций) потребует около двух лет.

5.9 Режим ответа на запрос AOR (бит 23)

Когда бит AOR в регистре конфигурации установлен, ATA5577C не переходит в режим регулярного чтения, после загрузки конфигурации из 0 блока. Тег ждет правильный AOR поток данных (команду пробуждения) от считывателя пока модулятор выключен. Команда "Пробуждения" состоит из кода операции ("10" или "11"), а затем пароль. Выбранная метка будет оставаться активной, пока поле не выключится или пока новая команда с другим паролем передается, которая может адресоваться к другой метке в поле.

| PWD | AOR | Поведение метки после команды сброса или POR (сброса по включению питания) | Функция деактивации |

|---|---|---|---|

| 1 | 1 | Режим ответа по запросу (AOR - Answer-On-Resquest):

|

Команда с неправильным паролем деактивирует выбранную метку |

| 1 | 0 | Режим пароля:

|

|

| 0 | – | Нормальный режим:

|

5.10 Расширенный режим

В целом, установка Master Key (биты 1-4) Блока 0 в значения 6(0110) или 9(1001) вместе с X-mode битом (15 бит) позволит использовать расширенные функции, такие как:

- режим двоичного переключения скорости генератора

- OTP функциональность

- режим быстрого входного протокола (Fast Downlink) (режим быстрой загрузки)

- инвертирование выходных данных

- возможность задавать (или помечать) стартовую последовательность

- Master Key = 9(1001): Поддерживается доступ и в тестовом режиме и в расширенном режиме.

- Master Key = 6(0110): Отключен любой доступ в тестовом режиме, но доступ в расширенном режим остается включенным.

Любые другие настройки Master Key будет препятствовать активации опций ATA5577C в расширенном режиме, даже когда X-mode бит установлен.

5.10.1 Режимы модулятора в расширенном моде (16-20 биты)

5.10.2 Режим двоичного переключения скорости генератора (биты 9-14)

В расширенном режиме скорость передачи данных программируется на любую четную скорость передачи данных от RF/2 до RF/128, в соответствии с указанной формулой.

BitRate (Скорость передачи данных) = RF/(2n + 2)

Значение n задаётся в битах 9-14 регистра конфигурации, может принимать значения от 0 до 63, при этом бит 9 - старший разряд, 14 - младший.

5.10.3 Функция OTP (однократно программируемая память) (24 бит)

Если бит OTP установлен в 1, все блоки памяти, защищены от записи и будут вести себя, как будто все Lock биты установлены в 1. Если, в дополнение к установленному биту OTP, значение поля master кey (мастер-ключ) = 6 (0110), то в этом случае режим работы ATA5577C нельзя изменить (функция однократного программирования).

Если поле master key (мастер-ключ) = 9 (1001), то при доступе в тестовом режиме можно изменить конфигурацию метки (т.е. в тестовом режиме можно перезаписывать биты блока конфигурации).

5.10.4 Режим быстрой загрузки (30 бит)

- В расширенном режиме при включенной быстрой загрузке, время между двумя паузами (в передачи несущей) снижается. В режиме протокола с фиксированной длинной бита, логический 0 (ноль) обычно кодируется 12-ю периодами, а лог. 1 (единица) кодируется 28 периодами несущей. При отсутствии паузы более чем 32 периода несущей после предыдущей паузы, ATA5577C в режиме протокола с фиксированной длинной бита выходит из режима приема данных (downlink mode) рис. 5-10.

Временные параметры режима быстрой загрузки для протокола

- long-leading-reference показаны на рис. 5-11.

- leading-zero-reference показаны на рис. 5-12.

- кодирования 1 из 4 показаны на рис 5-13.

5.10.5 Инвертирование выходных данных (31 бит)

В расширенном режиме (X-Mode), ATA5577C поддерживает инвертирование выходных данных.

- Если инвертирование данных включено, модулятор, как показано на рисунке 5-3, работает с инверсными данными (см. таблица 5-8).

- Эта функция поддерживается для всех основных типов кодирования.

5.11 Режим общения считыватель-метка

- Во время операции чтения (режим ответа), данные, хранящиеся в EEPROM циклически выдаются.

- Между контактами 1 и 2 катушки подключается резистивная нагрузка.

- Эта модуляция с помощью резистивной нагрузки может быть обнаружена на считывающем устройстве.

5.11.1 Режим цикличного чтения

- В режиме регулярного чтения данные из памяти передаются последовательно, начиная с первого бита блока 1 до 32 бита последнего блока (например, 7 блока). Номер последнего читаемого блока определяется полем MAXBLK в EEPROM в блоке 0. Когда последний блок данных указанный в MAXBLK прочитан, передача данных возобновляется с бита 1 блока 1.

Пользователь может число читаемых блоков в режиме цикличного чтения, установив MAXBLK между 0 и 7 (каждый из которых представляет восемь блоков данных):

- если MAXBLK=7, то читаются блоки с 1 по 7;

- если MAXBLK=1, то непрерывно передаётся только блок 1;

- если MAXBLK=0, то передается содержимое блока (0) конфигурации (который обычно не предаётся);

- В случае MAXBLK = 0 или 1, режим цикличного чтения (regular-read) нельзя отличить от режима чтения блока (block-read).

Каждый раз, когда ATA5577C входит в режим регулярного или поблочного чтения, первый бит, который передаётся, является логическим 0. Поток данных начинается с бита 1 блока 1 и продолжается до 32 бита блока MAXBLK, и в случае режима цикличного чтения повторяется непрерывно.

- Примечание: Это поведение отличается от оригинальной Atmel e555x, и помогает декодировать поток PSK-модулированных данных.

5.11.2 Режим поблочного чтения (Block-read Mode)

- Используя команды прямого доступа только адресованный блок читается повторно (многократно).

- Этот режим называется "Режим чтения блока/поблочного чтения (Block-read Mode)".

- Режим прямого доступа вводится путем передачи кода операции доступа к странице ("10" или "11"), одиночного 0 и 3-х бит адреса читаемого блока, когда метка находится в нормальном режиме.

- В режиме пароля (PWD бит установлен в 1), для прямого доступа к одному блоку необходим правильный 32-разрядный пароль, который передаётся после кода операции доступа к странице, за которым следует одиночный 0 и 3-х разрядный адрес блока.

- Если переданный пароль не совпадает с содержанием Блока 7, метка ATA5577C возвращается в режим регулярного чтения.

- Примечание 1: При обращении к блоку 0 из страницы 1 будут читаться данные блока конфигурации (блок 0, страниц 0).

- Примечание 2: При обращении к блокам 4-7 из страницы 1 все данные будут читаться нулями.

5.11.3 Непрерывная (Terminator) последовательность (в Basic режиме) (29 бит)

- Sequence terminator (ST) - специальная последовательность(патерн) затуханий, который вставляется перед первым блоком и может быть использована для синхронизация чтения ответа метки.

- Эта (ST) последовательность рекомендуется только для FSK и Манчестер кодирования.

- В основном режиме ST состоит из четырех битовых периодов.

- В течение первого и третьего битового периода, значение данных - 1.

- Во втором и четвёртом битовом периоде, модуляция выключена (при использовании манчестерского кодирования, включен).

- При Би-фазной модуляции данные в блоках должны быть зафиксированы. Начальные и конечные биты в сочетании с ST должны быть надежно определены.

- ST может быть разрешена путем установки (ST бита 29 (ST = 1)) в основном режиме (X-Mode = 0).

- В режиме регулярного чтения, ST вставляется в начале каждой последовательности из MAXBLK блоков.

- В режиме блочного чтения, после любой команды записи или прямого доступа, или если MAXBLK был установлен на 1, ST вставляется перед передачей выбранного блока.

- Примечание: Это поведение отличается от предыдущих ИС (e5551/T5551 Atmel, T5554). Для получения дополнительной информации обратитесь к соответствующим применению.

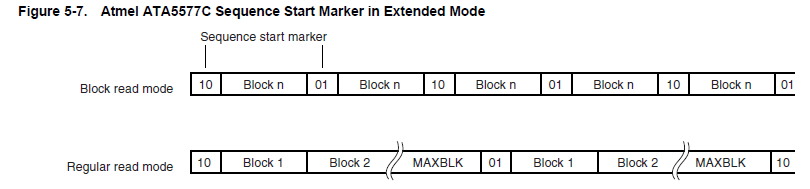

5.11.4 Последовательность Start Marker (бит 29 и X-Mode=1)

- Последовательность Start Marker в расширенном режиме (X-Mode) - специальная демпфирующие последовательность, которая может быть использован для синхронизация считывателя.

- Последовательность Start Marker состоит из двух бит ("01" или "10"), которые вставляются в качестве заголовка перед передачей первого блока, если в расширенном режиме (X-Mode=1), бит 29 установлен.

- Перед передачей нового блока, Start Marker биты инвертируются.

Режим общения считыватель-метка

- Данные передаются в тег путем прерывания ВЧ-поле короткими пробелами в поле (включение-выключение ключа) в соответствии с Atmel ®T5557/ATA5567 методом записи (нисходящий режим). Продолжительность этих пробелов, например, 100 мкс. Время между двумя пробелами кодирует передаваемый 0/1 (pulse interval encoding).

- Есть четыре различных протокола загрузки данных, который выбирается с помощью бит 21 и бит 22 в регистре конфигурации блока 3, страницы 1.

- Выбор по умолчанию протокола загрузки данных (протокол с фиксированной длиной бит), время между двумя пробелами номинально 24 такта для 0 и 56 такта для 1. При отсутствии зазора более 64 тактов после предыдущей паузы, ATA5577C выходит из режима приема (загрузки) данных.

- Тег начинает выполнять команду, если правильное число бит было получено.

- Если обнаружен какой-либо сбой, ATA5577C не выполняет команду, а после завершения посылки команды, входит в режим регулярного чтения.

- Улучшенная производительность загрузки данных может быть достигнута путем выбора само-калибрующихся протоколов загрузки. Atmel предлагает ATA5577C три различные возможности для достижения лучшей производительности с помощью само-калибрующихся протоколов загрузки:

- Длинная ведущая посылка: Полностью (в обоих направлениях) совместимый с бывшим метками и считывателями.

- Ведущий нуль: Считыватель должен отправить нуль перед потоком бит данных при загрузке. Этот нуль служит ориентиром для декодирования последующих нулей и единиц.

- 1-из-4 кодирование:Компактный протокол загрузки с оптимизированным балансом энергии.

Начальный интервал

Первичный интервал называют начальным интервалом. Он запускает обмен данными между считывателем и меткой. В регистре опций (блок 3, страница 1) можно выбрать несколько настроек, которые облегчают обнаружение интервалов в этом режиме работы; например, можно включить затухание при получении данных (смотрите таблицу 5-1 на странице 8). Возможно, потребуется, чтобы начальный интервал был длиннее последующих интервалов – так называемых интервалов записи – чтобы его можно было надежно обнаружить. Начальный интервал будет принят в любое время после загрузки регистра режима (около 3мс). Одиночный интервал не изменит ранее выбранную страницу (предыдущим кодом операции “10” или “11”).

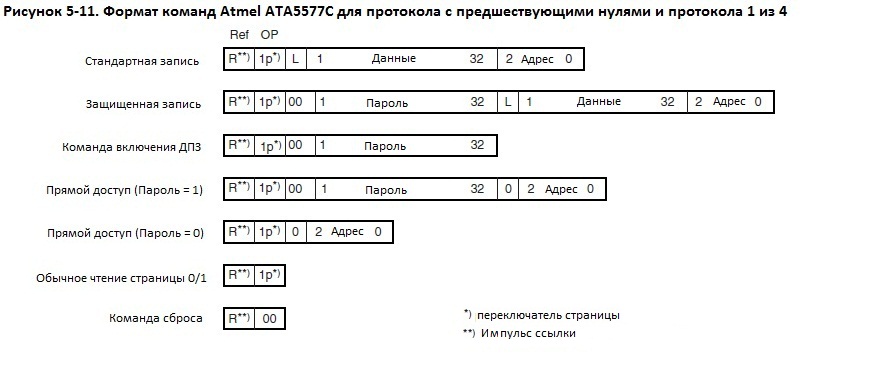

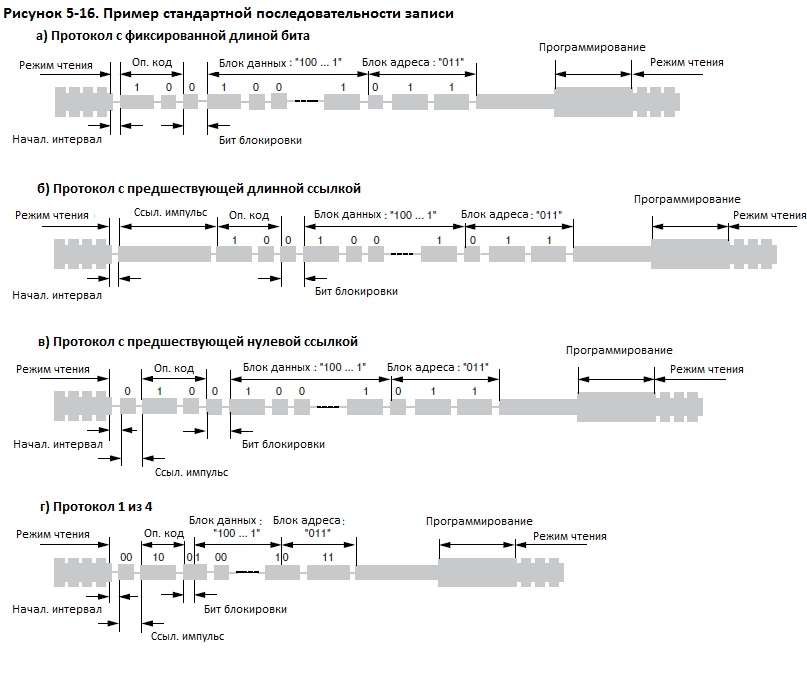

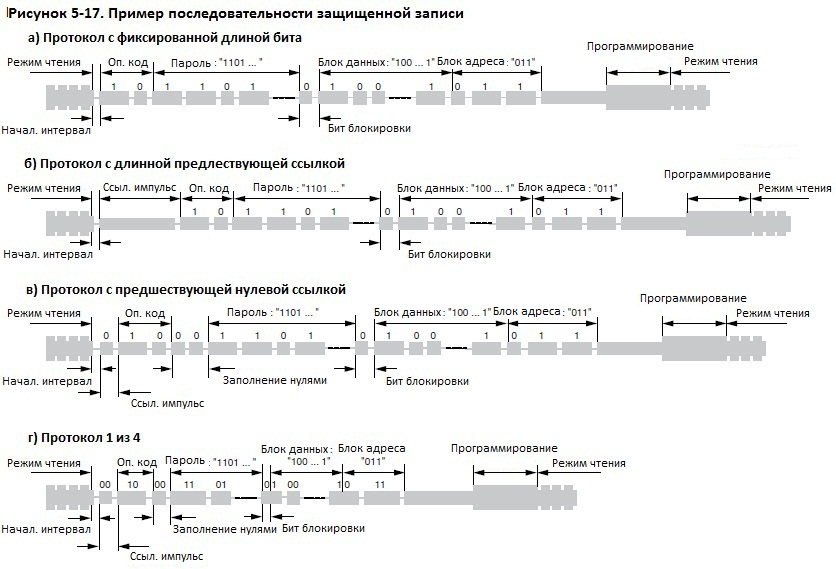

Формат команд

Формат входных данных

The Atmel® ATA5577C ожидает получить двухбитный операционный код как часть последовательности команды считывателя. Существует три правильных операционных кода:

- Операционный код «10» предшествует всем входным командам для страницы 0

- Операционный код «11» предшествует всем входным командам для страницы 1. Выполнение команды прямого доступа к блоку 0 всегда предоставляет блок 0 страницы 0 независимо от переключателя страниц (смотрите рисунок 4-2 на странице 6).

- Операционный код сброса «00» запускает цикл инициализации

Четвертый операционный код «01» предшествует всем операциям записи в тестовом режиме. Все операции доступа в тестовом режиме игнорируются, после того, как главный ключ (биты 1-4) в блоке 0 установлен в «6». Любые последующие изменения главного ключа запрещены установкой бита блокировки блока 0 или бита OTP. Входные операции должны следовать следующим правилам:

- Стандартная запись требует операционного кода, бита блокировки, 32 бита данных и 3 бита адреса (всего 38 бит)

- Защищенная запись (установлен бит пароля) требует правильного 32битного пароля между операционным кодом и битами данных и адреса. Защищенная запись (установлен бит пароля) вместе с протоколом предшествующих нулевых ссылок или с протоколом кодировки 1 из 4, требует прослойки в два нулевых бита между операционным кодом и паролем (смотрите также рисунок 5-17 на странице 24). Это обеспечивает уникальность прямого доступа с паролем и стандартной команды записи (смотрите также таблицу 6-1 на странице 25).

- Для команды включения режима Ответа по Запросу операционный код и правильный пароль необходимы для включения определенного передатчика.

Замечание: Биты данных читаются в той же последовательности, в которой они записаны. Если последовательность переданной команды неправильная, Atmel ATA5577C входит в режим обычного чтения с выбранной ранее страницей (предыдущим операционным кодом «10» или «11»).

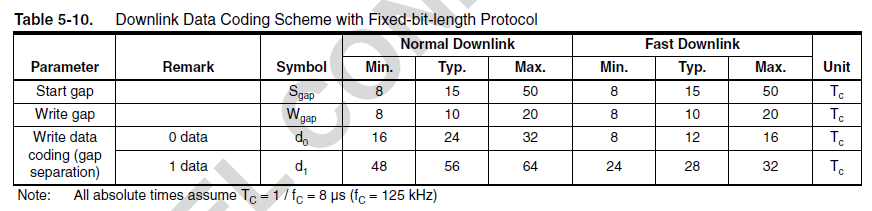

Протокол с фиксированной длиной бита

В протоколе с фиксированной длиной бита, время между двумя интервалами номинально составляет 24 field clocks для 0 и 56 field clock для 1. Если интервала нет более, чем 64 field clocks после предыдущего, Atmeil ATA5577C выходит из режима загрузки данных (в карту). Протокол совместим с передатчиком Atmel T5557/ATA5567.

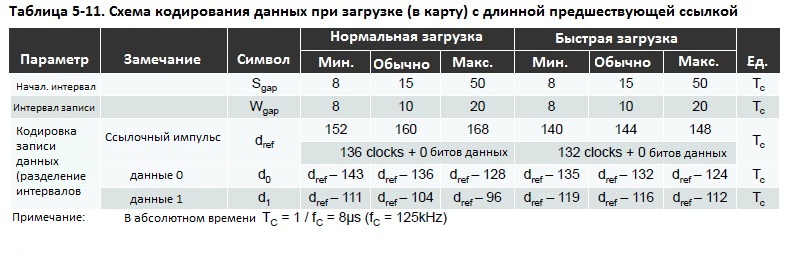

Протокол с предшествующей ссылкой чтения

Чтобы достичь лучшей производительности загрузки данных, расширенный считыватель Atmel® ATA5577C располагает импульс ссылки перед операционным кодом. Этот импульс ссылки используется в качестве временной ссылки для последующих данных, предоставляя авто-подстройку для различных условий среды. Протокол с длинной ссылкой чтения позволяет предоставляет полную совместимость и сосуществование устройств Atmel T5557/ATA5567 и Atmel ATA5577C, вместе с совместимыми с Atmel T5557/ATA5567 считывателями и усовершенствованными считывателями Atmel ATA5577C. Тем не менее, только устройства Atmel ATA5577C могут извлечь пользу из само-калибровки и увеличенной дистанции записи (смотрите таблицу 5-1 на странице 8 для настроек регистра опций). В этом режиме, проверяется импульс ссылки перед командой. В зависимости от длины импульса, остаток команды или проверяется с помощью протокола с фиксированной длиной бита, или используется в качестве ссылки измерения для оценки последующих битов команды. Иначе, последующие биты считаются неправильной командой.

- Для команды, основанной на ссылке, импульс ссылки (dRef) будет иметь длину от 16 до 32 + 136 = от 152 до 168 field clocks (нулевой бит + временное смещение = импульс ссылки). Следовательно, ожидаемая длина будет между 152 и 168 field clocks. Эквивалентная длина нулевого бита затем извлекается и используется в качестве ссылки для всех последующих битов. Импульс длиной предшествующей ссылки в этом случае используется только как временная ссылка и не входит в данные команды (смотрите рисунок 5-13, частично на странице 21).

- Если первый бит лежит внутри фрейма с фиксированной длиной бита (например в нормальное режиме 0: от 16 до 32 clocks; 1: от 48 до 64 clocks), устройство автоматически переключается на протокол с фиксированной длиной бита (смотрите Раздел Протокол с фиксированной длиной бита на странице 20) и первый импульс учитывается как первый бит команды. Это позволяет совместимость с длинной предшествующей ссылкой, запрограмированной устройствами Atmel ATA5577C с считывателями Atmel T5557/ATA5567 , которые не отправляют никаких импульсов ссылок (смотрите рисунок 5-13, часть б на странице 21).

- Если устройство Atmel T5557/ATA5567 работает с усовершенствованными считывателем Atmel ATA5577C, импульс ссылки (от 152 до 168 field clocks) игнорируется Atmel T5557/ATA5567 и последующие данные считаются правильными. Поэтому устройство Atmel T5557/ATA5567 совместимо с усовершенствованным считывателем Atmel ATA5577C (смотрите рисунок 5-13, часть б на странице 21).

- Если первый бит не отвечает ни за а), ни за б), он будет отклонен как неправильная команда.

Протокол с предшествующей нулевой ссылкой

Если устройство запрограммировано на этот режим, оно всегда ожидает ссылочный импульс перед данными самой команды. Длина этого импульса должна точно совпадать с длиной нулевых битов последующей команды.Все последующие длины битов нулей и единиц команды получаются из ссылочного импульса. Поэтому производительность загрузки данных (в карту) оптимальна для различных условий среды.

Протокол кодировки 1 из 4

Этот протокол кодирует данные парами битов, поэтому длина каждого пакета может иметь одно из четырех дискретных значений.Этот протокол очень компактный, и у него наименьшее количество полевых интервалов, что улучшает способность устройства извлекать питание из поля. Кроме того, пульс предшествующей ссылки «00» располагается впереди команды загрузки данных (в карту). Она служит ссылочным импульсом для всех последующих битов данных, предоставляя авто-регулировку для изменяющихся условий среды.

Программирование

Когда вся необходимая информация получена Atmel® ATA5577C, можно продолжить программирование. Между концом последовательности записи и началом программирования есть clock задержка. Обычно, время программирование равно 5.6мс. Этот цикл включает в себя проверку прочитанных данных для того, чтобы обеспечить безопасное и правильное программирование. После успешного выполнения программирования, Atmel ATA5577C входит в режим блокировки чтения, передавая только что запрограммированный блок (смотрите рисунок 5-18 на странице 25). Замечание: Время и поведения отличны для предшественников семьи Atmel e555x. Для дополнительной информации, смотрите соответствующие замечания Atmel. Если последовательность команды проверена и запрошенный блок не защищен от записи, новые данные запрограммируются в память EEPROM. Новое состояние бита блокировки записи (бит блокировки) будет в то же время соответствующе запрограммирован. Каждый цикл программирования состоит из четырех последовательных этапов: стереть данные блока, стереть проверку (данные = 0_, программирование, и проверка записи (соответствующие биты данных = 1).

Замечания: 1. Программирование страницы 1 с последующим одиночным интервалом приведет к чтению страницы 1. Чтобы войти в режим обычного чтения, необходимо произвести команду POR или Сброс.

Обработка ошибок

Можно проверить несколько условий на ошибки, чтобы быть уверенным, что только правильные биты программируются в EEPROM. Есть два типа ошибок, которые ведут к различным действиям.

Ошибки в последовательности команды

Следующие ошибки могут происходить вовремя отправки последовательности команды на Atmel® ATA5577C:

- Неправильное количество field clocks между двумя интервалами ( то есть неправильный поток импульса 1 или 0)*

- Включен режим пароля и пароль не совпадает с содержимым блока 7*

- Не правильное количество полученных битов последовательности команды.

Правильное количество битов для Atmel ATA5577C приведены в таблице ниже.*

Если зафиксированы любые из этих ошибочных условий (кроме режима AOR), Atmel ATA5577C входит в режим обычного чтения, начиная с блока 1 страницы, указанной в последовательности команды. Ошибочная команда включения AOR остановит модуляцию (ошибка модуляции).

Ошибки перед/во время программирования EEPROM

Если последовательность команды была успешно получена, следующие ошибки все равно могут помешать программированию:

- Бит блокировки блока, к которому обращается команда, уже установлен*

- Если блок заблокирован, устройство не войдет в режим программирования. Atmel® ATA5577C постоянно откатывается на режим блокировки чтения для блока, к которому идет обращение*

- Если обнаружена ошибка при проверке данных после выполненного программирования блока данных, карта прекратит модуляцию (ошибка модуляции), пока не будет передана новая команда.*

Идентификация животных

В ISO11784/11785 определена структура кода – телеграмма 128-bit FDX-B. Далее показано пример программирования Atmel ATA5577C для ISO 11785 FDX-B.

Замечания: *За исключением заголовка, после каждых восьми бит идет один бит управления (1), чтобы избежать повторения заголовка.*

- Все данные сначала передаются LSB.

- Коды стран определены в ISO 3166

- Биты, зарезервированные для будущего использования все установлены в 0.

- Если флаг блока данных не установлен, завершающие биты установлены в 0.

- CRC выполняется на 64-битном идентификационном коде без битов управления. Многочлен генератора:

P(x) = x16 + x12 + x5 + 1. Используется обратная CRC-CCITT (0x 8 408). Поток данных сначала в LSB.

Программирование Atmel® ATA5577C для идентификации животных:

- Кодировка данных - дифференциальная двухфазная RF/32

- 128 бит должны быть переданы в режим обычного чтения (Макс. Блок = 4)

Максимальные абсолютные номиналы

Нагрузки, выше приведенных ниже “Максимальных абсолютных номиналов” могут привести к полному выходу устройства из строя. Это номиналы только для нагрузки, и работа устройства при этих, или любых других условиях, выше указанных в секциях управления этой спецификации не предполагаются. Если подвергнуть устройство условиям максимального абсолютного номинала в течение продолжительного периода времени может повлиять на надежность устройства.

Электрические характеристики

Tamb = +25°C; fcoil = 125kHz; если не указано другое

- ) Тип означает: T: проверено напрямую или косвенно вовремя производства; Q: гарантирован на основании изначальных данных о качестве продукта

Замечания:

- 1. Установлено IDD измерение: EEPROM запрограммировано на 00 ... 000 (стереть все); карта в режиме modulation defeat.

- 2. Ток в катушках Coil1/Coil2 ограничен 10mA.

- 3.Так как на работу EEPROM влияют процессы сборки, Atmel не может подтвердить доставку параметры для -DDW (tested die on unsawn wafer).

- 4.Смотрите раздел 10. “Информация заказа” на странице 37.

Информация о заказе

Доступные коды заказа

- ATA5577M1330C-DDB

- ATA5577M1330C-DDT

- ATA5577M1330C-PAE

- ATA5577M1330C-UFQW

- ATA5577M1330C-PP

- ATA5577M133SC-DDB

- ATA5577M2330C-DBB

- ATA5577M2330C-DBQ

- ATA5577M2330C-DBN

- ATA5577M233AC-DBB

- ATA5577M233SC-DBB

Новые коды заказов будут созданы по запросу потребителя, если количество заказов превышает 250 тысяч штук.

Настройка при доставке

Таблица 10-1. Настройка при доставке

Информация о пакете

История ревизий

Обратите внимание, что следующие номера страниц, указанные в этом разделе ссылаются на конкретную указанную ревизию, а не на этот документ.