RFR (RFID READER)/Описание микросхемы FT2232H

- Спецификация программы

- Спецификация на считыватель

- Спецификация платы FT2232H

- Описание микросхемы FT2232H

- Тестовый план

Общее описание контактов

Секция представляет собой описание работы контактов микросхемы FT2232H. Функции множества контактов зависят от выбранного режима работы микросхемы. В таблице ниже представлено описание контактов в зависимости от выбранного режима (для сигналов с активным нулем используется пометка - имя_сигнала#). Пины отмеченные ** по умолчанию входы (inputs) с тремя состояниями и с внутренним резистором 75KΩ(примерно) подтягивающим вход к питанию VCCIO.

Также общие контакты. Они одинаково работают для любой конфигурации.

Описание режимов микросхемы

Режим RS232 интерфейса

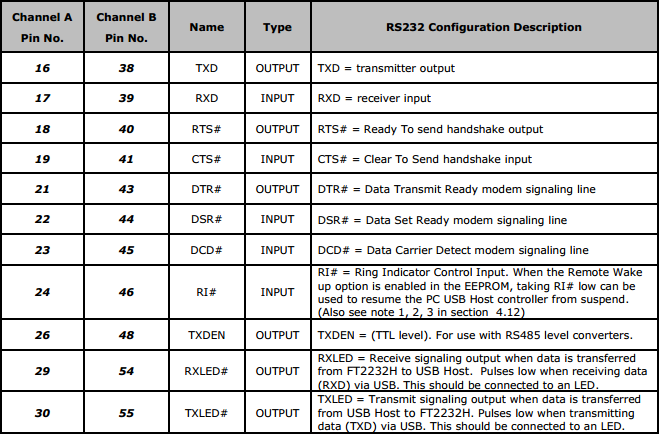

Канал А или Канал В микросхемы FT2232H могут быть сконфигурируемы как RS232 интерфейс. Таблица с контактами представлена ниже.

Режим синхронного FIFO интерфейса стиля FT245 (FT245 Style Synchronous FIFO Interface)

В качестве FT245 Style Synchronous FIFO Interface может быть сконфигурирован только Канал А. Что бы войти в этот режим необходимо установить внешний EEPROM что бы перевести порт А в режим 245. Затем к FTDI драйверу должна быть послана команда (Set Bit Mode option) из ПО что бы сказать чипу войти в режим single channel synchronous FIFO. В этом режиме Канал В не доступен, и все ресурсы передаются Каналу А. В этом режиме информация записывается или считывается по переднему фронту CLKOUT.

Режим асинхронного FIFO интерфейса стиля FT245 (FT245 Style Asynchronous FIFO Interface)

Канал А или Канал В могут быть настроены в качестве FT245 Style Asynchronous FIFO Interface. Что бы войти в этот режим необходимо установить внешний EEPROM что бы перевести порт А или В в режим 245. В этом режиме информация записывается или считывается по заднему фронту сигнала RD# или WR#.

Режим синхронного или асинхронного Бит-банг интерфейса (Synchronous or Asynchronous Bit-Bang Interface)

Канал А или Канал В могут быть настроены в качестве Synchronous or Asynchronous Bit-Bang Interface. Режим Бит-банг это специальный режим FTDI устройства FT2232H который меняет 8 входных/выходных линий одного (или обоих) канала на 8-ми битную двунаправленную шину данных. Есть два типа Бит-банг режима: синхронный и асинхронный.

Режим MPSSE

Канал А и Канал В на чипе FT2232H оба имеют Multi-Protocol Synchronous Serial Engine (MPSSE). Каждый MPSSE может быть независимо настроен на несколько стандартных последовательных протоколов, таких как JTAG, I2C или SPI, или может быть использован для применения проприетарного протокола шины. Например, возможно использовать один из каналов FT2232H что бы соединиться к SRAM-конфигурируемой FPGA, такой как поддерживаемая Altera или Xilinx. Устройство FPGA на момент включения обычно не настроена (т.е. без определенной функции). ПО на PC может использовать MPSSE что бы загрузить настроечную информацию на FPGA через USB. Эта информация определит аппаратную функцию при включении. Другой канал FT2232H будет доступен для другой функции. Также каждый MPSSE может быть использован для контроля нескольких контактов GPIO.

Режим быстрого последовательного интерфейса (Fast Serial Interface)

Канал В чипа FT2232H может быть настроен для использования с высоко-скоростной оптической двунаправленной изолированной последовательной передачей данных: быстрый последовательный интерфейс (high-speed optical bi-directional isolated serial data transfer: Fast Serial Interface). (Не доступно для Канала А). Проприетарный протокол FTDI разработан для возможности гальванических изолированных устройств (galvanic isolated devices) соединяться синхронно с FT2232H посредством только 4-х шин (над двумя двойными опто-изоляторами) (4 signal wires (over two dual opto-isolators)), и двух линий питания (power lines). Периферийные устройства управляют передачей данных, в то же время поддерживая полную целостность данных. Возможно достижение максимальной полной скорости передачи данных через USB (Maximum USB full speed data rates). При желании оба канала А и В могут передавать через те же 4-х шинные интерфейсы.

Режим FIFO интерфейса CPU стиля (CPU-style FIFO Interface)

канал А или Канал В могут быть настроены в режим CPU-style FIFO Interface, который позволяет CPU взаимодействовать с USB через FT2232H. Этот режим разрешен во внешнем EEPROM (This mode is enabled in the external EEPROM).

Режим Host Bus Emulation Interface

Чип FT2232H может быть использован что бы объединить Канал А и Канал В для настройки их в режим host bus emulation interface, который эмулирует стандартный 8048 или 8051 хост.

Выбор режима работы микросхемы

Выбор режима работы микросхемы осуществлялся из соображений удобства и доступности на плате (не все режимы доступны на плате, поскольку не все контакты чипа выведены на плату. Для выяснения доступности режимов использовался мануал плата FT2232H ). Был выбран режим MPSSE, что бы осуществлять передачу по протоколу JTAG. Потому что:

- это один из доступных режимов,

- JTAG - синхронный протокол,

- достигаемая по JTAG скорость передачи достигает 30 мбит/с. Это достаточная скорость.

- при передаче используется немного контактов, как следствие - удобная работа.

Описание выбранного режима

Режим MPSSE включается с помощью драйверной команды Set Bit Bang Mode. Шестнадцатеричное значение 2 включит, а Шестнадцатеричное значение 0 сбросит устройство. Для деталей и примеров смотри Заметку 01 .

Набор команд MPSSE полностью описан в Заметке 02 .

Для настройки MPSSE также доступны Заметка 03 , Заметка 04 и Заметка 05 .

Временные характеристики

Режим MPSSE разработан, что бы позволить FT2232H эффективно работать с синхронными последовательными протоколами, такими как: JTAG, I2C и SPI Bus. Также режим может быть использован для программирования SRAM-основанной FPGA через USB. Интерфейс MPSSE разработан быть гибким, что бы его можно было настроить на любой синхронный последовательный протокол. MPSSE доступен на Канале 1 и 2.

MPSSE полностью настраиваемый и запрограммирован посылкой команд по потоку данных. Они могут быть посланы индивидуально или более эффективно в пакетах. MPSSE способен на передачу данных со скоростью до 30 Мбит/сек.

Когда Канал настроен на MPSSE режим, ниже на рисунке и в таблице показаны тайминги и сигналы для CLKOUT = 30MHz. CLKOUT может быть внутренне поделен для более медленной частоты.

MPSSE Adaptive Clocking

Adaptive Clocking это новая фича MPSSE, добавленная к движку MPSSE FT2232H.

Этот режим эффективно связывает сигнал CLK с возвращаемым тактовым сигналом RTCK. Это возможность ARM процессоров.

FT2232H закрепит линию CLK и будет ждать возвращения RTCK из целевого устройства на линию GPIOL3 перед изменением TDO (линия выход данных).

Соединение Adaptive Clocking.

Сигналы Adaptive Clocking.

Adaptive Clocking по умолчанию отключен. Смотреть Заметку 02 .