ПТСиПЦУвСБ/Практическая работа 4 — различия между версиями

Материал из Wiki

ANA (обсуждение | вклад) м (→Уровень сложности 1) |

ANA (обсуждение | вклад) м (→Уровень сложности 1) |

||

| (не показаны 12 промежуточных версий 1 участника) | |||

| Строка 16: | Строка 16: | ||

=== Варианты заданий === | === Варианты заданий === | ||

| + | ==== Уровень сложности 0 ==== | ||

| + | |||

| + | Разработать синтезируемое VHDL-описание блока де/кодирования данных в заданном коде и тестовое окружение (testbenh) для проверки работы блока. | ||

| + | # Тип кодировки 1-256 ([[media:ISO15693-2.pdf|Стандарт ISO 15693-2 (pdf)]]). [[#Задание 1|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | # Тип кодировки 1-4 (iso-15693-2) [[Файл:ISO15693-2.pdf]]. [[#Задание 2|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | # Тип кодировки манчестер (iso-15693-2) [[Файл:ISO15693-2.pdf]]. [[#Задание 3|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | # Тип кодировки FM0 (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]]. [[#Задание 4|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | # Тип кодировки код Миллера (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]]. [[#Задание 5|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | # Тип кодировки iso-18000-6 [[Файл:Input_18000-6_(E)REV1_v62.pdf]]. [[#Задание 6|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | # Тип кодировки ATA-5575 [[Файл:Doc9167.pdf]]. [[#Задание 7|Описание задания]]. | ||

| + | ## блок кодирования данных; | ||

| + | ## блок декодирования данных. | ||

| + | |||

| + | Описание заданий приведено ниже. | ||

| + | |||

==== Уровень сложности 1 ==== | ==== Уровень сложности 1 ==== | ||

| Строка 31: | Строка 58: | ||

# таймер с выводом на семисегментный индикатор. | # таймер с выводом на семисегментный индикатор. | ||

# секундомер с выводом на семисегментный индикатор. | # секундомер с выводом на семисегментный индикатор. | ||

| + | # Преобразователь 8 битного двоичного кода в код Грея | ||

| + | #* входной код задаётся переключателями и выводится на семисегментный индикатор в 16-м виде | ||

| + | #* код Грея отображается на светодиодах | ||

| + | # Преобразователь 8 битного кода Грея в двоичный код | ||

| + | #* входной код Грея задаётся переключателями и выводится на семисегментный индикатор в 16-м виде | ||

| + | #* двоичный код отображается на светодиодах | ||

| + | # Световые эффекты на строке светодиодов (плавное управление яркостью бегущего огонька) | ||

==== Уровень сложности 2 ==== | ==== Уровень сложности 2 ==== | ||

| Строка 51: | Строка 85: | ||

# Калькулятор ([×|+|-]) в терминале. Задание входных и выходных данных и кода операции по интерфейсу RS232. (Например, набираешь в терминале "2+8=", после набора символа '=' из ПЛИС возвращается результат выражения. | # Калькулятор ([×|+|-]) в терминале. Задание входных и выходных данных и кода операции по интерфейсу RS232. (Например, набираешь в терминале "2+8=", после набора символа '=' из ПЛИС возвращается результат выражения. | ||

# Отобразить на экране монитора надпись "ПЦУСБ" через VGA интерфейс. | # Отобразить на экране монитора надпись "ПЦУСБ" через VGA интерфейс. | ||

| + | |||

| + | |||

| + | === Описание заданий уровня сложности 0 === | ||

| + | |||

| + | {{Info|Выбрать один из вариантов заданий (сообщить номер задания преподавателю лично или по эл. почте). Задания предполагают работу в паре, где один разрабатывает кодер, другой декодер для одного типа кодировки. Поэтому желательно выполнять задания в паре.}} | ||

| + | |||

| + | При выполнении заданий следует учитывать следующие общие требования: | ||

| + | # Разработать ''синтезируемое'' VHDL-описание блока. | ||

| + | #* Название entity - '''coder''', '''decoder'''. | ||

| + | #* Название architecture - '''beh'''. | ||

| + | #* Название портов in - '''D_I, clk, rst'''. | ||

| + | #* Название портов out - '''D_O'''. | ||

| + | #* Типы портов - std_logic[_vector]. | ||

| + | #* Внутренние сигналы называть так, чтобы было интуитивно понятно их названия. | ||

| + | #* Должна быть обеспечена возможность стыковки блоков кодирования и декодирования (по выводам) для совместной верификации (при выполнении работы в паре). | ||

| + | # Разработать тестовое окружение для запуска моделирования на языке VHDL. | ||

| + | #* Использовать структуру тестбенча (ТБ), описанную в [[ПЦУСБ/Лекция_6|лекции 6]]. ТБ включает блок кодирования, блок декодирования (при работе в паре), блок model, блок TestCtrl. | ||

| + | #* Название entity - '''tb'''. | ||

| + | #* Название architecture - '''beh'''. | ||

| + | #* Входные тесты (входные данные) должны читаться из файла, а выходные данные должны записываться в файл. | ||

| + | #** Функции чтения/записи из файла могут быть описаны по примеру из книги {{книга| автор = Бибило П.Н.| название = VHDL. Эффективное использование при проектировании цифровых систем| место = М.| издательство = СОЛОН-ПРЕСС| allpages = 344| isbn = 5-98003-293-2| год = 2006}}. | ||

| + | # Синтезировать полученную схему в программе ISE для базисе любой ПЛИС. | ||

| + | <!-- | ||

| + | #* для синтеза использовать: | ||

| + | #** библиотеку [[alib.syn]] логических элементов | ||

| + | #** скрипт для проведения синтеза [[syn.tcl]] | ||

| + | #* сохранить синтезированное (структурное) описание схемы | ||

| + | --> | ||

| + | #* Подготовить лог синтеза, в котором отображаются число элементов или площадь, и максимальное быстродействие схемы. | ||

| + | # Провести моделирование синтезированной схемы совместно с исходным описанием. | ||

| + | #* Модифицировать ТБ так, чтобы провести моделирование блоков кодирования/декодирования по исходным и синтезированным моделям одновременно. Сравнить эквивалентность функционирования двух VHDL-описаний блоков. | ||

| + | #* Для моделирования синтезированной схемы использовать VHDL-описание библиотеки логических элементов [[alib.vhd]]. | ||

| + | #* Привести отчет о покрытии кода (по всем видам). Покрытие исходного VHDL описания блоков кодирования/декодирования должно быть 100%. | ||

| + | # Использовать структуру папок проекта, описанную в [[ПЦУСБ/Лекция_6|лекции 6]]. Компиляция и запуск моделирования (до и после синтеза) должны быть автоматизированы с помощью соответствующих TCL-скриптов и BAT файлов. | ||

| + | |||

| + | |||

| + | =====Задание 1 ===== | ||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 1-1 | ||

| + | ! Задание 1-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | # Тип кодировки FM0 (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |||

| + | |- | ||

| + | |colspan=2| | ||

| + | |||

| + | {{Hider|Тип кодировки 1-256 ([[Файл:ISO15693-2.pdf|ISO 15693-2]]). Описание}} | ||

| + | {| class=standard align=center width=100% | ||

| + | !colspan=2| Тип кодировки 1-256 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:1-265_кодировка.jpg|600px|center]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_1-256_kod.jpg|500px|center]] | ||

| + | |||

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_1-256.jpg|300px|center]] | ||

| + | |} | ||

| + | {{Hider|end}} | ||

| + | |} | ||

| + | |||

| + | =====Задание 2===== | ||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 2-1 | ||

| + | ! Задание 2-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | |- | ||

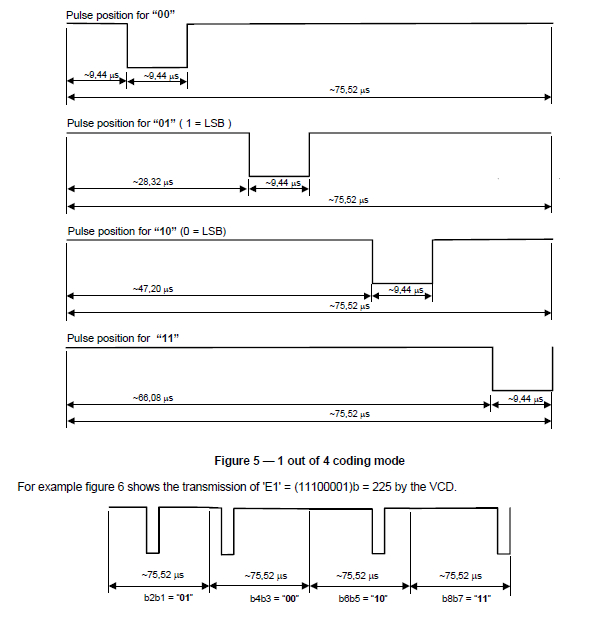

| + | !colspan=2| Тип кодировки 1-4 (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:1-4_кодировка.jpg|600px|center]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_1-4_kod.jpg|500px|center]] | ||

| + | |||

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_1-256.jpg|300px|center]] | ||

| + | |} | ||

| + | |||

| + | |||

| + | =====Задание 3===== | ||

| + | |||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 3-1 | ||

| + | ! Задание 3-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | # Тип кодировки код Миллера (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |||

| + | |- | ||

| + | !colspan=2| Тип кодировки манчестер (iso-15693-2) [[Файл:ISO15693-2.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Manchester_cod.jpg|600px|center]] | ||

| + | |||

| + | * Частота тактового сигнала 13.56 MHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_manchester_kod.jpg|600px|center]] | ||

| + | |||

| + | * После завершения передачи данных EOF | ||

| + | |||

| + | [[Файл:Eof_manchester_kod.jpg|600px|center]] | ||

| + | |} | ||

| + | |||

| + | |||

| + | =====Задание 4 ===== | ||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 4-1 | ||

| + | ! Задание 4-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |- | ||

| + | !colspan=2| Тип кодировки FM0 (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:FM0_кодировка.jpg|600px|center]] | ||

| + | |||

| + | |- | ||

| + | |colspan=1| | ||

| + | * Число передаваемых данных задается generic паратмером NUM_SEND_BIT | ||

| + | | | ||

| + | * Число принимаемых данных задается в generic параметре NUM_GET_BIT! | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | * Частота тактового сигнала 1.98 MHz | ||

| + | * Частота закодированных данных 640 KHz | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | |||

| + | [[Файл:Sof_FM0_kod.jpg|300px|center]] | ||

| + | |||

| + | |- | ||

| + | |colspan=1| | ||

| + | * После завершения передачи данных, посылать EOF | ||

| + | | | ||

| + | * Прекращать прием после прихода символа EOF или после получения заданного числа бит. | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Eof_FM0.jpg|450px|center]] | ||

| + | |} | ||

| + | |||

| + | |||

| + | =====Задание 5 ===== | ||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 5-1 | ||

| + | ! Задание 5-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных. (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок записи принимаемых данных в файл. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Входной порт DATA_I, для принимаемых от кодера данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | |- | ||

| + | !colspan=2| Тип кодировки код Миллера (iso-18000-6) [[Файл:ISO18000-6REV1v62.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Миллер_кодировка.jpg|500px|center]] | ||

| + | [[Файл:Миллер кодировка состояния.jpg|200px|center]] | ||

| + | |||

| + | |- | ||

| + | | | ||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | | | ||

| + | * Число принимаемых данных задается в generic параметре NUM_GET_BIT! | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | |||

| + | * Частота тактового сигнала 1.98 MГц | ||

| + | * Частота закодированных данных 320 кГц (два такта выходной частоты на один бит данных, см. рис.) | ||

| + | |- | ||

| + | | | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | | | ||

| + | * Прием данных начинать после получения SOF | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Sof_миллер_kod.jpg|350px|center| Символ SOF]] | ||

| + | |- | ||

| + | | | ||

| + | * После завершения передачи данных посылать EOF | ||

| + | | | ||

| + | * Прекращать прием после прихода символа EOF или после приема NUM_GET_BIT | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | |||

| + | [[Файл:Eof_миллер.jpg|500px|center|Символ EOF]] | ||

| + | |||

| + | |} | ||

| + | |||

| + | =====Задание 6===== | ||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 6-1 | ||

| + | ! Задание 6-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Входной порт DATA_I, для принимаемых от кодера данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |- | ||

| + | !colspan=2| Тип кодировки iso-18000-6 [[Файл:Input_18000-6_(E)REV1_v62.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Input_18000_кодировка.jpg|400px|center]] | ||

| + | |- | ||

| + | | | ||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | | | ||

| + | * Число принимаемых данных задается в generic параметре NUM_GET_BIT! | ||

| + | |- | ||

| + | | | ||

| + | * Частота тактового сигнала 8 MHz | ||

| + | | | ||

| + | * Частота тактового сигнала 1.92 MHz | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | * Tari= 6.25us (см. рис.) | ||

| + | * RTcal= (Data-0) + (Data-1)=3 * Tari = 18.75us | ||

| + | |- | ||

| + | | | ||

| + | * Перед стартом передачи данных посылать SOF | ||

| + | | | ||

| + | * Данные декодировать после получения SOF | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Sof input 18000 kod.jpg|400px|center]] | ||

| + | |- | ||

| + | | | ||

| + | * Завершение передачи данных после посылки NUM_SEND_BIT бит данных. | ||

| + | | | ||

| + | * Полученный символ кодирует 1, если его длинна больше RTcal/2, если меньше, то кодирует логический 0. | ||

| + | * Завершение передачи данных после посылки NUM_SEND_BIT бит данных. | ||

| + | |} | ||

| + | |||

| + | |||

| + | =====Задание 7===== | ||

| + | |||

| + | {| class=standard | ||

| + | ! Задание 7-1 | ||

| + | ! Задание 7-2 | ||

| + | |- | ||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока кодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |||

| + | | | ||

| + | # Разработать синтезируемое VHDL-описание блока декодирования данных. | ||

| + | ## Входные порты: D_I, clk, rst. | ||

| + | ## Выходные порты: D_O, возможно добавление доп. сигналов обратной связи. | ||

| + | # Разработать тестовое окружение для запуска моделирования и проверки корректности передаваемых данных (Можно на SystemC, можно и на VHDL). | ||

| + | ## Тестовое окружение содержит в себе блок чтения данных из файла и подачи данных на D_I. | ||

| + | ## Блок формирования тактового сигнала. | ||

| + | ## Блок формирования сигнала сброса по питанию. | ||

| + | ## Выходной порт DATA_O, для выдачи закодированных данных | ||

| + | # Запуск моделирования, добавления сигналов и выполнение должны быть автоматизированны (script). | ||

| + | |- | ||

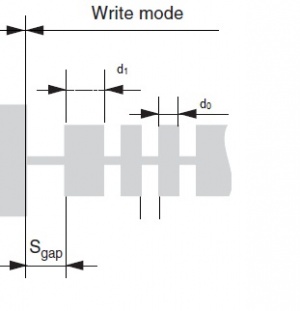

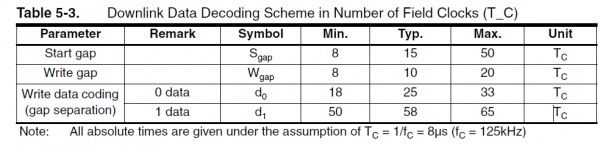

| + | !colspan=2|Тип кодировки ATA-5575 [[Файл:Doc9167.pdf]] | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Wrie_mode_raduga1.jpg|300px|center]] | ||

| + | |- | ||

| + | | | ||

| + | * Число передаваемых данных задается в generic параметре NUM_SEND_BIT ! | ||

| + | | | ||

| + | * Число передаваемых данных задается в generic параметре NUM_GET_BIT ! | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | * Частота тактового сигнала 125 кГц | ||

| + | * Для кодирования данных смотри таблицу | ||

| + | |- | ||

| + | | | ||

| + | * Старт передачи данных - первая пауза. | ||

| + | | | ||

| + | * Старт приема данных - первая пауза D_I равен 0. | ||

| + | |- | ||

| + | |colspan=2| | ||

| + | [[Файл:Wrie_mode_raduga1_table.jpg|600px|center]] | ||

| + | |- | ||

| + | | | ||

| + | * Завершение передачи данных после посылки NUM_SEND_BIT бит данных. | ||

| + | | | ||

| + | * Завершение приема данных после получения NUM_GET_BIT бит данных. | ||

| + | |} | ||

Текущая версия на 15:17, 14 апреля 2014

Лекции ПТСиПЦУвСБ

Лекции

Практические

- Практическая работа 1

- Практическая работа 2

- Практическая работа 3

- Практическая работа 4

Тесты

Лабораторные

Доп. материалы

Содержание |

Доступное оборудование

Варианты заданий

Уровень сложности 0

Разработать синтезируемое VHDL-описание блока де/кодирования данных в заданном коде и тестовое окружение (testbenh) для проверки работы блока.

- Тип кодировки 1-256 (Стандарт ISO 15693-2 (pdf)). Описание задания.

- блок кодирования данных;

- блок декодирования данных.

- Тип кодировки 1-4 (iso-15693-2) Файл:ISO15693-2.pdf. Описание задания.

- блок кодирования данных;

- блок декодирования данных.

- Тип кодировки манчестер (iso-15693-2) Файл:ISO15693-2.pdf. Описание задания.

- блок кодирования данных;

- блок декодирования данных.

- Тип кодировки FM0 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf. Описание задания.

- блок кодирования данных;

- блок декодирования данных.

- Тип кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf. Описание задания.

- блок кодирования данных;

- блок декодирования данных.

- Тип кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf. Описание задания.

- блок кодирования данных;

- блок декодирования данных.

- Тип кодировки ATA-5575 Файл:Doc9167.pdf. Описание задания.

- блок кодирования данных;

- блок декодирования данных.

Описание заданий приведено ниже.

Уровень сложности 1

- Преобразователь 8-ми разрядного числа из двоичного кода в двоично-десятичный код с отображением на семисегментном индикаторе в десятичном виде

- a) Преобразователь 10-разрядного числа из двоичного кода в двоично-десятичный код с отображением на 4-х позиционном семисегментном индикаторе в десятичном виде с последовательным вводом двоичного числа.

- Преобразователь числа из двоично-десятичного кода в 8-ми разрядный двоичный код с отображением на линейке светодиодов

- входной код отображается на семисегментном индикаторе в десятичном виде

- выходной код отображается на линейке светодиодов

- Калькулятор (4-разрядное число [×|+|-] 4-разрядное число)

- значения входных аргументов задаётся переключателями, при этом эти значения отображаются в шестнадцатеричном виде на семисегментном индикаторе (первых два индикатора)

- значение результата вычислений отображается в шестнадцатеричном виде на семисегментном индикаторе (вторые 2 индикатора)

- выполняемая арифметическая операция задаётся кнопками, при этом на светодиодах фиксируется номер операции.

- часы с выводом на семисегментный индикатор.

- таймер с выводом на семисегментный индикатор.

- секундомер с выводом на семисегментный индикатор.

- Преобразователь 8 битного двоичного кода в код Грея

- входной код задаётся переключателями и выводится на семисегментный индикатор в 16-м виде

- код Грея отображается на светодиодах

- Преобразователь 8 битного кода Грея в двоичный код

- входной код Грея задаётся переключателями и выводится на семисегментный индикатор в 16-м виде

- двоичный код отображается на светодиодах

- Световые эффекты на строке светодиодов (плавное управление яркостью бегущего огонька)

Уровень сложности 2

- Функция "Эхо" для терминала. Т.е. получение байта с компьютера по RS232 и отправка его обратно в ПК.

- Отобразить на экране монитора шахматную доску через VGA интерфейс.

- Термометр на основе температурного сенсора (DS18B20, 1-WIRE) с выводом значения на семисегментный индикатор либо на ЖКИ дисплей.

- Калькулятор с клавиатурой (матрица 4×4 кнопки) с отображением на светодиодном (4-х позицонном) или ЖКИ дисплее:

- Операции (+|–|÷|×|...) над целыми числами;

- Операции (+|–|÷|×|...) над целыми и вещественными числами;

- Тригонометрические операции (sin|cos|tg|ctg|...) над целыми и вещественными числами;

- Редактор текста с вводом с клавиатуры (PS/2)

- с выводом на ЖКИ дисплей LCD12864 (128×64 пикселей);

- с выводом в терминал по протоколу RS232.

- часы реального времени (PCF8563 RTC Board) с выводом на семисегментный индикатор либо на ЖКИ дисплей.

- дополнительные функции: таймер, секундомер, будильник и др.

Уровень сложности 3

- Калькулятор ([×|+|-]) в терминале. Задание входных и выходных данных и кода операции по интерфейсу RS232. (Например, набираешь в терминале "2+8=", после набора символа '=' из ПЛИС возвращается результат выражения.

- Отобразить на экране монитора надпись "ПЦУСБ" через VGA интерфейс.

Описание заданий уровня сложности 0

При выполнении заданий следует учитывать следующие общие требования:

- Разработать синтезируемое VHDL-описание блока.

- Название entity - coder, decoder.

- Название architecture - beh.

- Название портов in - D_I, clk, rst.

- Название портов out - D_O.

- Типы портов - std_logic[_vector].

- Внутренние сигналы называть так, чтобы было интуитивно понятно их названия.

- Должна быть обеспечена возможность стыковки блоков кодирования и декодирования (по выводам) для совместной верификации (при выполнении работы в паре).

- Разработать тестовое окружение для запуска моделирования на языке VHDL.

- Использовать структуру тестбенча (ТБ), описанную в лекции 6. ТБ включает блок кодирования, блок декодирования (при работе в паре), блок model, блок TestCtrl.

- Название entity - tb.

- Название architecture - beh.

- Входные тесты (входные данные) должны читаться из файла, а выходные данные должны записываться в файл.

- Функции чтения/записи из файла могут быть описаны по примеру из книги Бибило П.Н. VHDL. Эффективное использование при проектировании цифровых систем — М.: СОЛОН-ПРЕСС, 2006. — 344 p. — ISBN 5-98003-293-2..

- Синтезировать полученную схему в программе ISE для базисе любой ПЛИС.

- Подготовить лог синтеза, в котором отображаются число элементов или площадь, и максимальное быстродействие схемы.

- Провести моделирование синтезированной схемы совместно с исходным описанием.

- Модифицировать ТБ так, чтобы провести моделирование блоков кодирования/декодирования по исходным и синтезированным моделям одновременно. Сравнить эквивалентность функционирования двух VHDL-описаний блоков.

- Для моделирования синтезированной схемы использовать VHDL-описание библиотеки логических элементов alib.vhd.

- Привести отчет о покрытии кода (по всем видам). Покрытие исходного VHDL описания блоков кодирования/декодирования должно быть 100%.

- Использовать структуру папок проекта, описанную в лекции 6. Компиляция и запуск моделирования (до и после синтеза) должны быть автоматизированы с помощью соответствующих TCL-скриптов и BAT файлов.

Задание 1

| Задание 1-1 | Задание 1-2 | ||||

|---|---|---|---|---|---|

|

| ||||

|

Тип кодировки 1-256 (Файл:ISO15693-2.pdf). Описание

| |||||

Задание 2

| Задание 2-1 | Задание 2-2 |

|---|---|

|

|

| Тип кодировки 1-4 (iso-15693-2) Файл:ISO15693-2.pdf | |

| |

Задание 3

| Задание 3-1 | Задание 3-2 |

|---|---|

|

|

| Тип кодировки манчестер (iso-15693-2) Файл:ISO15693-2.pdf | |

| |

Задание 4

| Задание 4-1 | Задание 4-2 |

|---|---|

|

|

| Тип кодировки FM0 (iso-18000-6) Файл:ISO18000-6REV1v62.pdf | |

|

|

| |

|

|

Задание 5

| Задание 5-1 | Задание 5-2 |

|---|---|

|

|

| Тип кодировки код Миллера (iso-18000-6) Файл:ISO18000-6REV1v62.pdf | |

|

|

| |

|

|

|

|

Задание 6

| Задание 6-1 | Задание 6-2 |

|---|---|

|

|

| Тип кодировки iso-18000-6 Файл:Input 18000-6 (E)REV1 v62.pdf | |

|

|

|

|

| |

|

|

|

|

Задание 7

| Задание 7-1 | Задание 7-2 |

|---|---|

|

|

| Тип кодировки ATA-5575 Файл:Doc9167.pdf | |

|

|

| |

|

|

|

|