Проектирование цифровых систем на языках описания аппаратуры/Лекция 1

- Заголовок

- Введение в курс

- Автор

- Ланкевич Ю.Ю.

- Нижний колонтитул

- Проектирование цифровых систем на языках описания аппаратуры/Лекция 1

- Дополнительный нижний колонтитул

- Ланкевич Ю.Ю., 18:44, 18 октября 2020

Слайд:Цели и задачи курса

Изучить методы и компьютерные средства

- алгоритмического, функционального и структурного описания цифровых систем на формальных языках проектирования на примере языка VHDL

- моделирования проектов цифровых систем и устройств

- верификации проектов цифровых систем и устройств

- схемной реализации проектов цифровых систем и устройств.

Общая информация

Для оценки сложности интегральных схем используется единица эквивалентного вентиля (например 2-входовый И-НЕ), который соответствует 4-м эквивалентным транзисторам. Уровни интеграции цифровых интегральных схем принято делить на следующие группы:

- SSI - Small scale integration или МИС - малая интегральная схема с десятками и сотнями эквивалентных вентилей.

- MSI - Medium scale integration или СИС - средняя интегральная схема с тысячами вентилей.

- LSI - Large scale integration или БИС - большая интегральная схема с сотнями тысяч вентилей.

- VLSI – Very large scale integration или СБИС - Сверхбольшая Интегральная Схема с несколькими миллионами вентилей.

- USLI – Ultra large scale integration или УБИС - УльтраБольшая Интегральная Схема.

Наибольшее распространение на данный момент имеют СБИС, поэтому далее мы будем пользоваться этим термином для обозначения всех интегральных схем высокой степени интеграции.

Кроме того интегральные схемы условно делятся на группы специализированных применений (ASIC - Application Specific Integrated Circuit) и коммерческие интегральные микросхемы общего применения, как массовые микропроцессоры и серийные наборы микросхем. С развитием технологий производства и повышением степени интеграции появилось такое понятие как системы на кристалле (СнК) или Systems-on-Chip (SoC), которые представляют собой комбинацию специализированных и универсальных процессорных ядер и блоков, выполненных на единой кремниевой подложке.

СБИС также различаются по полупроводниковой технологии исполнения:

- TTL или ТТЛ - транзисторно-транзисторная логика на биполярных транзисторах

- ECL или ЭСЛ - эмиттерно-связанная логика

- MOS - NMOS, CMOS или МОП, НМОП и КМОП логика.

Слайд: Основные типы СБИС, используемые в электронной индустрии

- Полнозаказные СБИС (Full-Custom ASICs)

- Полузаказные матричные СБИС на основе стандартных ячеек-модулей (StandardCell–Based ASICs)

- Полузаказные СБИС на основе матрицы вентилей (Gate-Array–Based ASICs)

- Канальные матрицы вентилей (Channeled Gate Array)

- Бесканальные матрицы вентилей (Channelless Gate Array), наиболее популярные в настоящее время

- Структурированные матрицы вентилей (Structured Gate Array)

- СБИС программируемой логики c макроячейками или макроблоками (Complex Programmable Logic Devices or CPLDs) или ПЛИС

- СБИС программируемой логики c микроячейками или базовыми блоками (FieldProgrammable Gate Arrays or FPGA)

Каждый тип СБИС имеет свою нишу на рынке, которая определяется массовостью применения приборов

и изделий, а также степенью универсальности характеристик СБИС.

Все эти типы СБИС различаются стоимостью проектирования и изготовления, в случае ПЛИС разработчик использует готовые СБИС, программируя их

для своих приложений, что дает минимальную цену подготовки производства, которую называют

NRE – non-recurring engineering cost.

Слайд: Основные типы СБИС, используемые в электронной индустрии

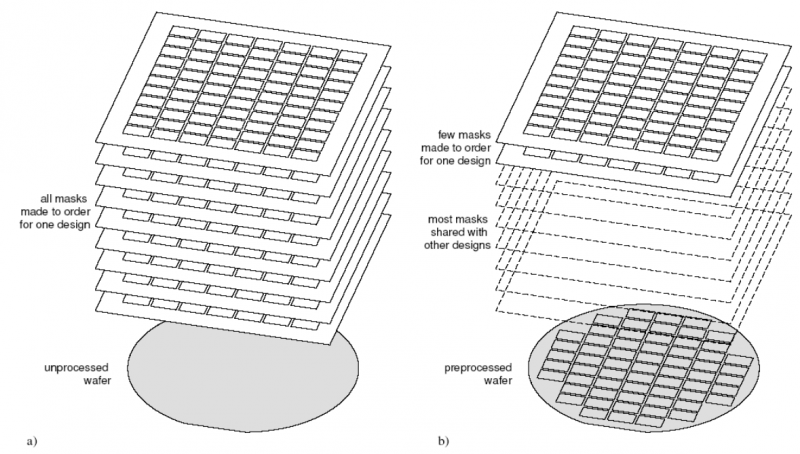

На рисунке ниже приведены наборы масок (называемых также фотошаблонами) для полнозаказных и полузаказных СБИС,

по их требуемому числу можно легко определить трудоемкость разработки каждого типа СБИС.

Самые нижние маски определяют

формирование базовых транзисторов на кремниевой подложке, следующие уровни определяют их топологические соединения металлическими проводниками для формирования базовых логических элементов и макро-блоков. Верхние уровни масок определяют межсоединения между крупными макроблоками и конфигурацию ввода-вывода. В современных технологических процессах производства полупроводников использутся свыше сорока масок, определяющих транзисторы, слои металлизации и изоляции. Стоимость комплекта масок достигает миллиона долларов и выше для процессов 45нм, а для 10нм достигает десятков миллионов долларов.

Слайд:Основные характеристики полностью заказных СБИС

(Full-Custom ASICs)

- Все слои масок полностью заказные, могут быть использованы для производства только этой конкретной СБИС

- Разработчик должен спроектировать топологию каждого вентиля своими руками (без использования стандартных библиотек)

- Возможны частично автоматизированное размещение и трассировка

- Критические пути проектируются практически вручную или с использованием специального инструментария, управляемого уникальными скриптами разработчика

- Полностью заказное проектирование СБИС дает возможность получить наиболее высокую производительность и минимальную цену кремния (меньший размер чипа) для конкретной разработки

- Недостатками заказной разработки СБИС являются длительное время разработки (годы для больших процессоров), сложность и дороговизна процесса разработки, а также наиболее высокий риск (ошибки и задержки)

Обычно микропроцессоры раньше выполнялись в виде полностью заказных СБИС, но сейчас проявляется массовая тенденция использования технологий проектирования полузаказных СБИС, особенно в системах на кристалле. Другими примерами полнозаказных микросхем являются специализированные схемы для высоковольтной логики (автомобили), аналого-цифровые схемы (коммуникации), датчики и микромеханизмы, также как динамическая память DRAM.

Слайд:Основные характеристики полузаказных СБИС на основе стандартных элементов ячеек (Standard-Cell-Based ASICs)

- Используется также аббревиатура CBIC —“sea-bick (Сell-based ASIC)

- Используются библиотеки стандартных элементов

- Возможно использование предварительно спроектированных мега-ячеек, мегафункций, полнозаказных мега-ячеек, системных макросов, блоков с фиксированными функциями, готовых процессорных ядер (IP-ядер) от других поставщиков, или стандартных функциональных блоков

- Все слои масок являются заказными – размещение транзисторов и все соединения между ними

- Автоматизированное изменение размерности буферов, размещение блоков и трассирование межсоединений

- Полнозаказные блоки легко могут быть встроены в структуру СБИС без проблем (если спроектированы под ту же технологию)

- Ориентировочное время производственного цикла с момента получения топологии в виде GDS файла около восьми недель

Этот тип полузаказных СБИС является базовой кремниевой платформой для современных систем на кристалле (СнК или SoC).

Так как с точки зрения свободы размещения блоков и макроблоков этот тип СБИС близок к полнозаказной и отличается только использованием заранее спроектированных библиотечных элементов и макроблоков, то размещение базовых транзисторов может быть совершенно произвольным и определяется макрокомпоновкой топологии полузаказной СБИС. Библиотечные элементы-ячейки в такой СБИС могут располагаться в виде матрицы, имеющей определенное число строк и столбцов, пресечениями которых являются логические элемент-ячейки. Между строками и столбцами могут оставляться пространства (каналы) для разводки межсоединений. И полузаказная структура СБИС строится путем соединения этих ячеек-элементов в логические схемы в соответствии с принципиальной схемой логического устройства, оформленной в виде списка логических сетей в формате EDIF или структурного кода VHDL/Verilog.

Слайд:Основные характеристики полузаказных СБИС на основе матрицы вентилей (GateArray–Based ASICs)

В матрице вентилей позиции всех транзисторов на пластине предопределены нижними слоями топологических масок, которые являются общими для всех вариантов СБИС. Эта предопределенная топология размещения транзисторов называется базовой матрицей, поэтому такие СБИС часто называют базовыми матричными кристаллами (БМК).

- Наименьший элемент, который повторяется в матрице, называется базой или ячейкой-примитивом

- Верхние уровни соединений между транзисторами определяются разработчиками СБИС в заказных масках верхнего уровня для формирования матрицы вентилей – Masked Gate Array (MGA)

- Проектирование выполняется путем соединения предпроектированных и заранее верифицированных библиотечных логических элементов (макроблоков)

После предварительной проверки реализуемости СБИС на уровне библиотечных элементов и макроблоков используется, как правило, автоматическое размещение и трассировка для преобразования в топологию СБИС с использованием ячеек-примитивов базовой матрицы.

Существуют три типа базовых матричных СБИС:

- Канальные матричные СБИС (Channeled Gate Array)

- Бесканальные матричные СБИС (Channelless Gate Array)

- Структурированные матричные СБИС (Structured Gate Array)

Слайд:Основные характеристики полузаказных СБИС на основе матрицы вентилей (GateArray–Based ASICs)

Особенности канальных матричных СБИС (Channeled Gate Array)

- Разработчиком проектируются только межсоединения между вентилями и соответственно изготовляются только верхние слои масок

- Межсоединения используют изначально предопределенны промежутки (каналы) между линейками базовых элементов

- Так как могут быть использованы предобработанные пластины с выполненными нижними слоями топологии, то резко снижается время прои который может длиться от двух дней до двух недель в зависимости от числа заказных верхних слоев металлизации межсоединений

Особенности бесканальных матричных СБИС (Channelless Gate Array)

- Их также называют «Море вентилей» (Sea-of-Gates)

- В таких матричных кристаллах нет предопределенных промежутков для трассирования межсоединений, межсоединения идут поверх базовых элементов матрицы

- Достижимая плотность размещения логических блоков значительно выше по сравнению с канальными матричными СБИС, что приводит к уменьшению кристалла

- Так как могут быть использованы предобработанные пластины с выполненными нижними слоями топологии, то резко снижается время производственного цикла СБИС, который может длиться от двух дней до двух недель в зависимости от числа заказных верхних слоев металлизации межсоединений.

Особенности структурированных матричных СБИС (Structured Gate Array)

- Заказчик проектирует только межсоединения вентилей матрицы

- Полнозаказные блоки могут быть встроены в конкретный вариант СБИС (для всей серии, имеющей определенную структуру)

- Это могут быть функционально завершенные блоки как процессоры, разного рода контроллеры или модули памяти

- И/или это могут быть матрицы базовых вентилей другого типа, которые больше подходят для выполнения специфической функции

- Длительность производственного цикла структурированной матричной СБИС от двух дней двух недель в зависимости от числа заказных верхних слоев металлизации межсоединений.

Слайд:Основные характеристики полузаказных СБИС на основе матрицы вентилей (GateArray–Based ASICs)

На рисунке ниже приведена структура матрицы вентилей с выделенными каналами для межсоединений, бесканальной и структурированной матрицы ветелй (A, B и C соответственно).

Основные характеристики СБИС программируемой логики

Программируемые СБИС c встроенными макроблоками (Complex Programmable Logic Devices - CPLD)

Этот тип программируемых СБИС имеет следующие особенности:

- Не нужно проектировать топологию межсоединений базовых элементов и макроблоков и можно обойтись без полупроводникового производства

- Все межсоединения программируются непосредственно на СБИС, которая доступна для приобретения и немедленного использования

- Очень быстрый цикл проектирования

- На СБИС имеется специальный большой блок для обеспечения программируемых межсоединений в жесткой (маскируемой) и мягкой (перепрограммируемой) вариации

- Стираемая программируемая СБИС (Erasable PLD -EPLD)

- Единожды программируемая с помощью маски (Mask-programmed PLD), которая обычно используется для массовых заказов у производителя

- Матрица логических макроблоков обычно содержит логические матрицы логических элементов, комбинируемых с линейками триггеров или регистров-защелок.

Программируемые СБИС c встроенными базовыми блоками (Field Programmable Gate Array – FPGA)

Этот тип программируемых СБИС имеет следующие особенности:

- Не нужно проектировать маску межсоединений, она программируема непосредственно на СБИС

- Поставщик СБИС предлагает метод и инструментальные средства программирования как базовых логических блоков, так и межсоединений между ними

- Ядром СБИС является регулярная матрица программируемых базовых логических блоков, которая может выполнять как логические функции и, так и функции фиксации данных в последовательной логике (триггерах) и блоках памяти

- Матрица программируемых межсоединений окружает элементы матрицы бпазовых логических блоков и обеспечивает их соединение друг с другом при программировангии конфигурации СБИС

- Программируемые блоки ввода-вывода окружают матрицу логических базовых блоков

- Процесс проектирования можно завершить за несколько часов

На рисунке ниже представлена структура программируемой СБИС c встроенными базовыми блоками (FPGA) и структура программируемой СБИС с встроенными макроблоками (CPLD).

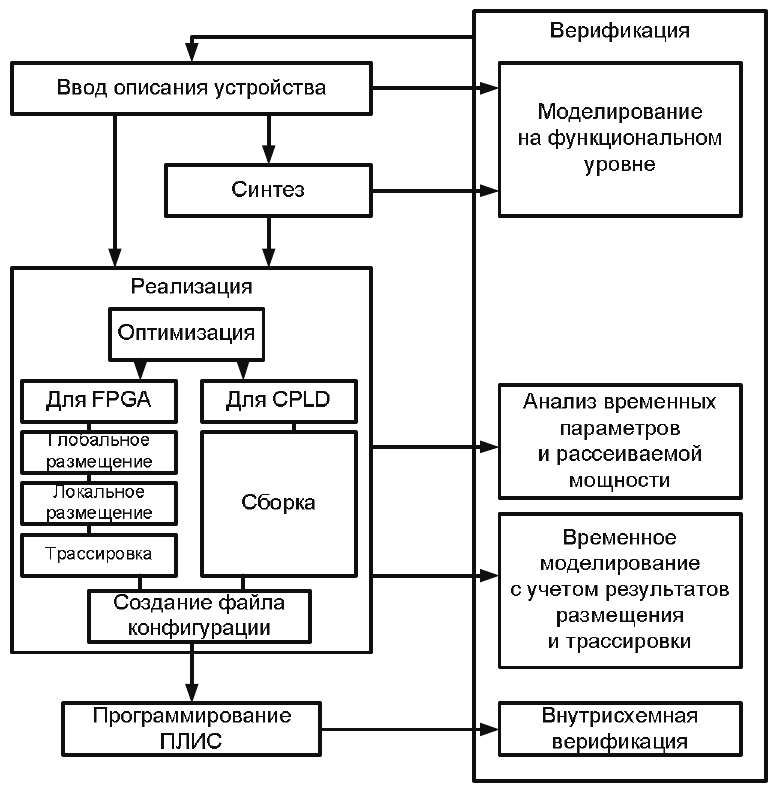

Слайд: Маршрут проектирования ЦС

Рассмотрим упрощенный маршрут проектирования СБИС, который включает ряд этапов, взаимосвязь которых отображена на рисунке ниже. В реальности маршрут проектирования выглядит сложнее, но в любом случае он содержит верификацию, логическое проектирование СБИС (front-end design) и физическое проектирования СБИС (back-end design).

Слайд: Логическое проектирование

Этап описания логических схем (не учитывается технология, физические,электрические и другие характеристики). Описывается комбинационная логика, триггеры и связи между элементами схемы. Для описания используются такие языки, как VHDL, Verilog, SystemC. Результатом является логическая схема на уровне регистровых передач (RTL).

В данном этапе можно выделить нексолько дополнительных шагов:

- Формальное описание проекта (Design entry) – Проектирование СБИС осуществляется с использованием либо разработанной принципиальной схемы, либо языка моделирования аппаратных средств (Verilog, VHDL, SystemC). В обоих случаях используются специальные срества САПР от производителей Сadence, Synopsys, Mentor Graphics.

- Логический синтез (Logic synthesis) – Средства САПР от производителей, указанных выше обеспечивают генерацию списка логических вентилей и их межсоединений (netlist)

- Разбиение на модули (System partitioning) – Большая система (top level) разбивается на модули (sub-system level), которые в свою очередь могут быть разбиты на ещё более мелкие блоки (block level).

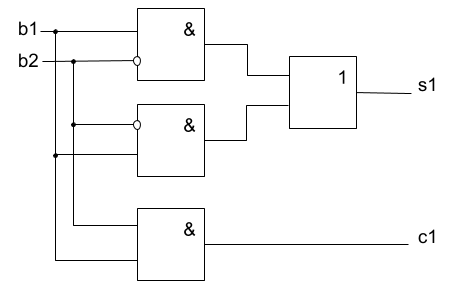

Слайд:Пример использования языков описания аппаратуры

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ TestBench

entity Test_add1 is end Test_add1; architecture Behavior of test_add1 is component add1 port (b1,b2 : in BIT; -- в VHDL не различаются строчные c1,s1 : out BIT); -- и прописные буквы end component; signal b1, b2 : BIT; signal c1, s1 : BIT; begin p1 : add1 port map (b1 => b1, b2 => b2, c1 => c1, s1 => s1); b1 <= '1', -- входные воздействия '0' after 50 ns, '1' after 100 ns, '0' after 150 ns, '1' after 200 ns; b2 <= '1', -- входные воздействия '1' after 50 ns, '1' after 100 ns, '0' after 150 ns, '0' after 200 ns, '1' after 250 ns; end behavior; --------------------------------------------------

Тестирующая программа для проверки правильности VHDL-модели полусумматора представляет собой текстовый файл test_add1.vhd. Файл test_add1.vhd находится в директории D:/Petrov, который называется рабочим директорием (директорием проекта)

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim от Mentor Graphics/ Создание проекта в системе моделирования

После запуска программы ModelSim SE 6.1b открывается основное окно системы

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/

Создание проекта в системе моделирования

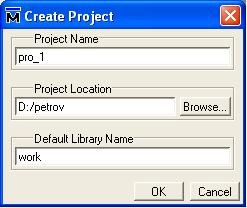

В главном меню выбираем File → New → Project. Появится окно Create Project Указание имени проекта, места расположения проекта, имени рабочей библиотеки.

- В окне Project Name укажем имя проекта ( pro_1)

- В окне Project Location укажем рабочий директорий (d:/petrov )

- В окне Default Library Name оставим имя work.

- Нажмем OK.

Строго рекомендуется для рабочей библиотеки указать имя work, предлагаемое по умолчанию.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/

Добавление файлов в проект

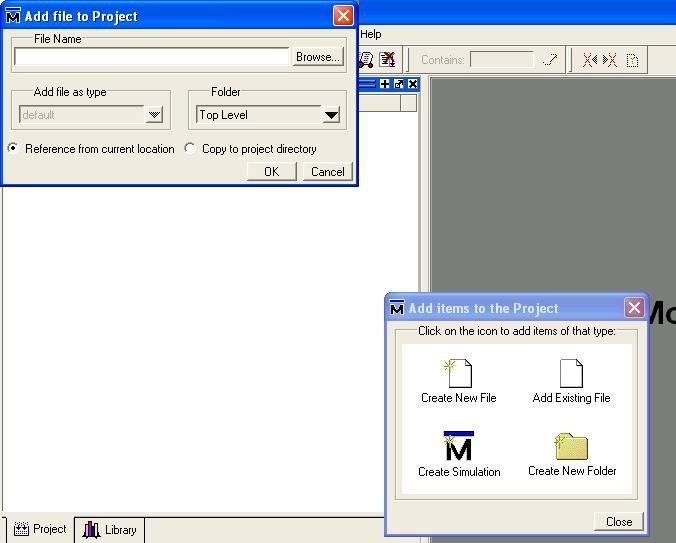

В окне Add Items to the Project выбираем “Add Existing File”, так как VHDL-файлы с описанием цифрового дизайна и тестбенча уже имеются.

Они находятся в директории проекта d:/petrov.

После выбора Add Exiting File появится окно Add file to Project

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/

Добавление файлов в проект

По очереди (с помощью Browser) находим в директории d:/petrov файл add1.vhd (VHDL-модель) и файл test_add1.vhd (VHDL-тест)

и добавляем их в проект (можно отметить несколько файлов и одновременно добавить их в проект). В окне Workspace поочередно,

в порядке их добавления, появляются имена добавляемых файлов, составляющих проект.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/

Компиляция проекта

В главном меню выбратьм Compile → Compile Order , появится окно Compile Order.

Рекомендуется выбрать Auto Generate и нажать OK. Если программы не содержат ошибок,

то в окне Workspace напротив имен файлов знак вопроса после компиляции заменяется “птичкой”.

В этом окне можно вручную установить порядок компиляции файлов:

компиляция осуществляется согласно иерархии описания проекта – сначала на компиляцию должны поступать

- описания пакетов (в примере их нет),

- затем листовые описания (в примере это описание add1.vhd),

- затем описания, содержащие листовые описания, и т.д. (других листовых описаний нет),

- последнее описание – это тестирующая (головная) VHDL-программа (test_add1.vhd).

Если программа содержит ошибку, то в нижнем окне Transcript выдается сообщение. Двойной щелчок на сообщении об ошибке выдает строку VHDL-текста, в которой может быть ошибка (однако на самом деле ошибка может быть совершенно в другой строке – синтаксис VHDL сложный!!!). Выдача текста VHDL-программы для редактирования осуществляется двойным щелчком по имени соответствующего VHDL-файла.

Если программы не содержат ошибок, то в нижнем окне Transcript появляются соответствующие сообщения. В примере это сообщения

# vcom_capture -work work -2002 -explicit D:/petrov/add1.vhd # Compile of add1.vhd was successful. # vcom_capture -work work -2002 -explicit D:/petrov/test_add1.vhd # Compile of test_add1.vhd was successful.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Задание опций моделирования

Выбрать в главном меню Simulate → Runtime Options, появится окно Runtime Options. Задать:

- Default Radix → Symbolic (формат представления данных),

- Default Run → 100 ns (время одного шага моделирования при пошаговом моделировании),

- Iteration Limit → 5000 (число событий моделирования, событие – изменение сигнала).

Остальное – по умолчанию, нажать OK

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Старт симуляции

Выбрать в главном меню Simulate → Start Simulation, появится окно Start Simulation Раскрыть библиотеку work, выбрать (двумя щелчками) имя головной программы (test_add1), остальное – по умолчанию. Нажать OK.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование /

Закладка sim в окне Workspace

Правильный результат выполнения старта моделирования, проект для моделирования прочитан без ошибок

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Открытие окна Objects

В главном меню View → Debug Windows → Objects установить флаг (птичку) Objects, откроется окно Objects. Из этого окна мышью можно будет перетащить отдельные требуемые для наблюдения сигналы в окно Wave. Это окно может быть открыто командой View → Debug Windows → Wave.

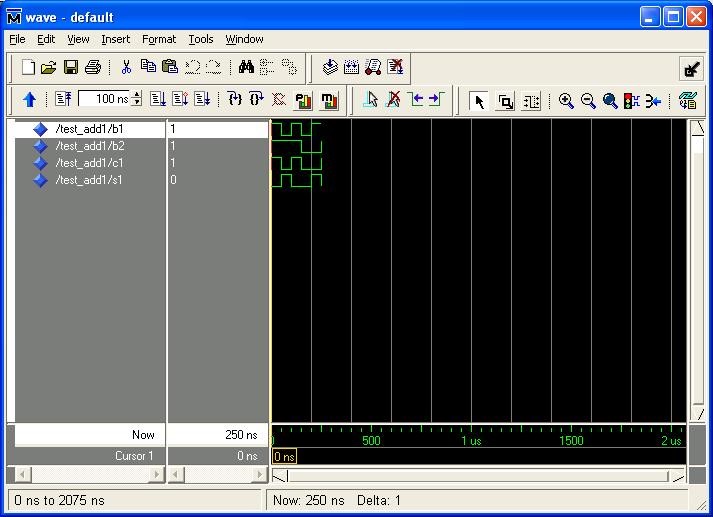

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Перемещение всех сигналов в окно Wave

В окне Objects в меню выполнить Add → Wave → Signals in Region. В результате все сигналы из окна Objects повторятся в окне Wave. Откроется окно Wave, появятся соответствующие команды в нижнем окне Transcript. Это есть другой способ перемещения сигналов из окна Objects в окно Wave.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Остановка бесконечного цикла моделирования

Выполнить команду (Run All) в окне Wave, получить возможно визуально “сжатую” временную диаграмму, которую сложно воспринимать. Остановить бесконечное (зациклившиеся) моделирование можно командой break в консольной области (окно Transcript), либо командой главного меню Simulate → Break, либо нажатием кнопки (Break) в окне Wave. В случае цикла текущее время моделирования непрерывно увеличивается. Текущее время выводится внизу окна Wave. ! Опасность бесконечного цикла состоит в том, что результат моделирования (файл временной диаграммы) “забьет” все свободное место на жестком диске. Удалить такой файл бывает трудно.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Изменение масштаба времени

Чтобы “разжать” временную диаграмму, можно воспользоваться командами "Zoom In"/"Zoom Out" изменения масштаба времени. Выполнив одну из команд "Zoom In"/"Zoom Out", получим “читаемую” временную диаграмму.

Слайд: Пример маршрута симуляции цифровой схемы в ModelSim/ Моделирование / Результаты работы

Временную диаграмму можно сохранить и распечатать по команде Print. При выходе из системы моделирования в рабочем директории появятся:

- директорий work (в нем скомпилированные во внутреннее представление файлы проекта);

- системный файл pro_1.mpf сохраненного проекта цифровой системы (двойной щелчок вызовет систему моделирования и загрузит сохраненное состояние проекта);

- системный файл vsim.wlf временной диаграммы (двойной щелчок вызовет систему моделирования и откроет окно wave с сохраненной временной диаграммой).

При завершении работы в системе ModelSim директорий проекта запоминается и в следующем сеансе можно начать работу с проектом, выполнив команду File → Recent Directories и выбрав соответствующий рабочий директорий, либо выполнив команду File → Recent Project, выбрав ранее сохраненный проект

Слайд: Верификация

Этап проверки соответствия описания логических схем спецификации.

Актуальные проблемы верификации

- размер объекта верификации постоянно растет. Даже небольшая ИМС типа “микроконтроллер” — это набор из десятков подмодулей, очень часто со сложным функционалом. Большие ИМС — это комплексы, в которых может насчитываться до десятков миллиардов транзисторов, и одна только схема управления электропитанием по сложности может превосходить некоторые процессоры;

- высокая цена ошибки (от десятков тысяч долларов до десятков миллионов долларов);

- невозможно составить спецификацию на ИМС в начале проекта и в дальнейшем только следовать ей, она постоянно изменяется на протяжении всего процесса разработки (заказчик изменяет требования, технические проблемы или обнаружение более оптимальных решений вынуждают пересматривать подходы и т.д.). Исходя из этого, * все процессы должны в динамике воспринимать изменения спецификации и модифицироваться в соответствии с требованиями;

- часто над верификацией проекта работает несколько удаленных друг от друга команд численность которых может достигать десятков человек;

- количества отдельных тестов и их типов достигает огромного числа, результаты их надо собирать и анализировать;

- моделирование цифровых систем требует много машинного времени и вычислительных ресурсов;

- полнота установленных для проекта целевых показатели готовности во многом зависит от компетентности и интуиции специалистов по верификации;

- несмотря на существование показателей охвата проекта тестами (метрик), единственный способ закончить верификацию — это принять решение о ее приостановке, основываясь в основном на следующих заключениях: деньги или время на этап проекта потрачены, необходимо запускать в производство, вроде как достигли покрытия кода в 100%, тестируем уже неделю и ошибок не обнаружили и т.п.

Для целей верификации часто используются такие языки как SystemVerilog, SystemC, VHDL, specman E. Для каждого из перечисленных языков существуют стандартные фреймворки (библиотеки).

- SystemVerilog: VMM, OVM, UVM.

- VHDL: OSVVM, UVVM.

- SystemC: UVM.

- Specman E: UVM.

Верификацию можно разделить на следующие шаги:

- Функциональная верификация (Functional Verification) – проверка всех функциональных параметров и характеристик СБИС на логическом уровне. Если моделирование не дает корректных результатов, то этап логического проектирования (исправление ошибок проектирования) повторяется до достижения успеха.

- Формальная верификация (Formal Verification) - устанавливается эквивалентность представлений системы на разных стадиях маршрута проектирования или выполнение утверждений, помещенных в исходный код:

- Equivalence Checking (например, RTL-to-RTL, RTL-to-Gate, Gate-to-Gate);

- Property Checking (Model Checking) - проверяет свойства(assertions), заданные в коде средствами SVA (SystemVerilog Assertions) или PSL (Property Specification Language).

- Cтатический анализ кода (static code analysis) — проверка исходного кода по формальным критериям на соблюдения правил использования языка и его конструкций. Программы для такой проверки обычно обозначаются как lint или linter;

- Прототипирование — использование FPGA для функциональной проверки.

- Физическая верификация — в основном подразумевается DRC, LVS, PERC и пр. проверки, физическое представление системы проверяется на соблюдение технологических норм и соответствия физического и логического представлений и т.д. Состав проверок сильно зависит от технологии. Обычно физическая верификация проводится инженером или командой топологического проектирования

Функциональная верификация в объеме всех работ наиболее значительна и требует непосредственного участия человека. Статический анализ кода требуют только первоначальной настройки инструментов, которая соответствует внутренним правилам проектирования, принятым в компании, дальше данный инструмент можно использовать без дополнительных трудозатрат. Инструменты формальной верификации часто тоже весьма самостоятельны, требует только внимательного анализа отчетов, которые они генерируют.

Методы функциональной верификации

Типы метрик функциональной верификации

Слайд:Физическое проектирование

Этап построения топологии цифровой схемы (размещение логических элементов и проводников на поверхности кристалла) для конкретного технологического процесса с учётом всех производственных норм и характеристик Результатом является файл топологии интегральной схемы GDS II, который отправляется на фабрику.

Физическое проектирование можно разбить на следующие шаги:

- Топологическое размещение (Floorplanning) – Размещение модулей и блоков из списка логических вентилей и соединений на площади кристалла СБИС.

- Размещение базовых элементов внутри блоков (Placement) – Выбор размещения базовых библиотечных элементов в блоках.

- Трассирование и разводка межсоединений (Routing) – Соединение базовых библиотечных элементов, модулей и блоков между собой.

- Экстракция паразитных сопротивлений и емкостей межсоединений (Extraction) – Определяются паразитные емкости и сопротивления, порождаемые спроектированной топологией межсоединений.

- Postlayout simulation – Проверяется работоспособность будущей СБИС с добавленной паразитной нагрузкой на межсоединения. Если они не удовлетворяют требованиям по частоте и нагрузке, то предыдущие шаги повторяются до получения требуемого результата.

рамках этапов физического моделирования производится также проверка соблюдения правил дизайна для технологии, по которой будет производиться СБИС (design rule check – DRC), также производится процесс обратной экстракции принципиальной схемы из физического топологии и используемых библиотек и производится сверка с исходной принципиальной схемой (netlist). Такая проверка называется сверкой топологии с принципиальной схемой (layout versus schematic check- LVS).

Слайд: Маршрут проектирования с использованием ПЛИС (Xilinx)

Слайд: Литература

- http://vhdl.bas-net.by/

- А. К. Поляков, Языки VHDL и VERILOG в проектировании цифровой аппаратуры

- П. Н. Бибило, Основы языка VHDL