Проектирование цифровых систем на языках описания аппаратуры/Лекция 3

- Заголовок

- Основы языка VHDL. часть 2

- Автор

- Ланкевич Ю.Ю.

- Нижний колонтитул

- Проектирование цифровых систем на языках описания аппаратуры/Лекция 3

- Дополнительный нижний колонтитул

- Ланкевич Ю.Ю., 11:30, 21 сентября 2020

Слайд:Логические элементы

В алгебре логики известны три основные логические операции:

- Логическое умножение (конъюнкция или операция И). Записывается как F = A Λ B, F = A & B, F = A·B, F = AB, читается – A и B.

- Логическое сложение (дизъюнкция или операция ИЛИ). Записывается как F = A V B, F = A | B, F = A+B, читается – F = A или B.

- Логическое отрицание (инверсия или операция НЕ). Записывается F = A , читается – F = “не” A.

Слайд:Таблица истинности логических элементов

| Аргументы | Логические операции (булевы функции) | ||||

|---|---|---|---|---|---|

| А | В | И | ИЛИ | НЕ | |

| A·B | A+B | A | B | ||

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

| Операторы VHDL | A and B | A or B | not A | not B | |

Комментарий

Таким образом, выполнение сколь угодно сложной логической операции может быть сведено к трем вышеперечисленным операциям. Следовательно, имея некоторые технические устройства, реализующие операции И, ИЛИ, НЕ, можно построить сколь угодно сложное цифровое устройство. Такие устройства называются соответственно логическими элементами И, ИЛИ, НЕ и образуют основной базис или функционально полную систему логических элементов.

Слайд:Арифметические и логические операции

Набор операторов (операций) в VHDL обеспечивает возможность работы с предусмотренными типами данных. Список операций приведен в таблице ниже. Строки таблице располагаются в порядке приоритетов (от низшего к высшему) операторов. Операторы, находящиеся в одной строке, обладают одинаковым приоритетом. Таким образом, операции нижней строки обладают наибольшим приоритетом и выполняются первыми.

Исходя из контекста VHDL-кода следует отличать оператор <= (назначение сигнала) и оператор <= (меньше либо равно). Следует также отличать унарные операции присвоения знака +, - от соответствующих бинарных операций сложения и вычитания. Для устранения неоднозначностей трактовки старшинства операций используются скобки. Например, выражение "A nand B nand C" неверно (синтаксическая ошибка). Данное выражение не представляет трехвходовый элемент И-НЕ (трехвходовую NAND-ячейку). Правильная запись "not (A and B and C) ". Запись "A nand (B nand C)" не есть то же самое, что "(A nand B) nand C".

Операции языка VHDL:

| Приоритет | Классы операторов |

Обозначение | Название |

|---|---|---|---|

| 0 (низкий) | Логические | and or nand nor xor xnor |

логическое И логическое ИЛИ логическое И-НЕ логическое ИЛИ-НЕ исключающее ИЛИ эквивалентность |

| 1 | Отношения | = < > <= >= /= |

равно меньше больше меньше либо равно больше либо равно не равно |

| 2 | Сдвиги (VHDL 2008, определены для std_logic_vector) | sll srl sla sra rol ror |

логический сдвиг влево логический сдвиг вправо арифметический сдвиг влево арифметический сдвиг вправо циклический сдвиг влево циклический сдвиг вправо |

| 3 | Сложение | + – & |

сложение + вычитание - конкатенация |

| 4 | Унарные | +, – | присвоение знака + присвоение знака - |

| 5 | Умножение | * / mod rem |

умножение деление модуль остаток |

| 6 (высокий) | Вспомогательные | ** abs not |

возведение в степень абсолютное значение логическое НЕ |

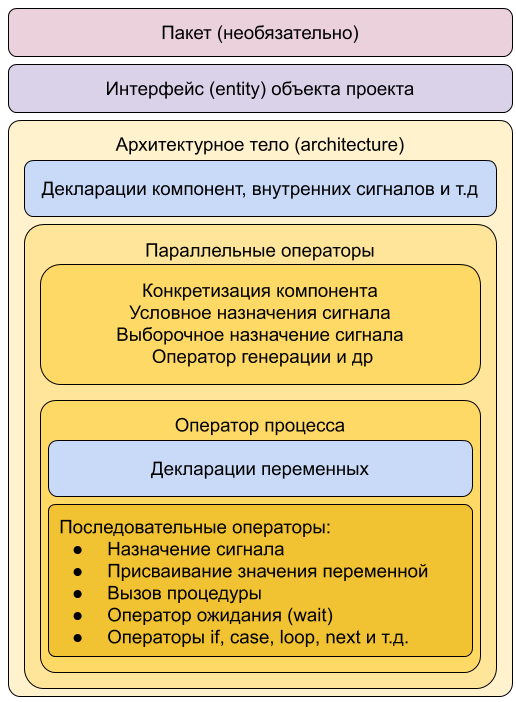

Слайд:Структура VHDL описания

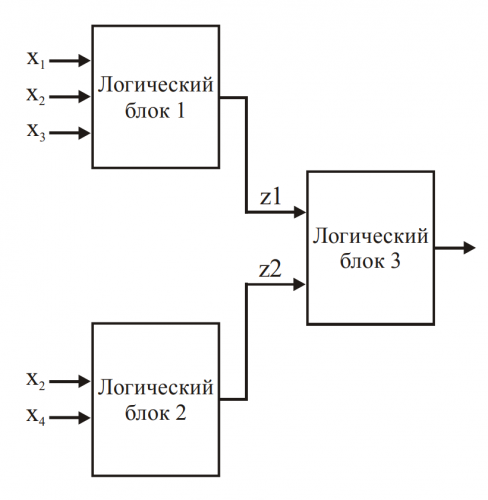

Слайд:Пример параллельных процессов в логической схеме

На схеме ниже показаны три логических блока. Если предположить, что входной набор 1 (для логического блока 1) и входной набор 2 (для логического блока 2) изменяются одновременно, то выходы логических блоков 1, 2 будут изменяться также одновременно. Выход логического блока 3 будет изменяться чуть позже, в то время как через блоки 1, 2 могут проходить (конвейерным способом) измененные значения сигналов других входных наборов. Таким образом, поток сигналов может проходить через все блоки одновременно.

Слайд:Параллельные процессы и параллельные операторы

В языке VHDL процесс активизируется, когда происходит изменение какого-либо сигнала в списке сигналов запуска этого процесса (или в списке чувствительности (sensitivity list)). В общем случае список сигналов запуска содержит входной набор сигналов соответствующего логического блока.

Рассмотрим схему с монтажным соединением выходных полюсов элементов.

! Можно определять только по одному драйверу на сигнал в процессе.

Так как в каждом процессе сигнал должен иметь только один источник, то, в случае, если имеется несколько источников сигнала, требуется специальная (разрешающая) функция, которая будет вычислять значение сигнала по значениям этого сигнала из нескольких драйверов.

Например, сигнал Y имеет два источника, и, соответственно, два драйвера. Для такого сигнала требуется разрешающая функция. Подробнее эта проблема будет рассмотрена далее.

Слайд:Параллельные процессы и параллельные операторы

Параллельные операторы в VHDL определяют параллельное (во времени) поведение схем.

! Порядок выполнения параллельных операторов не связан с порядком их появления внутри архитектурного тела.

Параллельные операторы активизируются сигналами, которые употребляются для связи параллельных операторов. Последовательные операторы выполняются в порядке их появления в VHDL-коде.

Параллельные операторы: 1. оператор process (процесс); 2. оператор параллельного сообщения; 3. оператор параллельного вызова процедуры; 4. оператор условного назначения сигнала; 5. оператор select выборочного назначения сигнала; 6. оператор конкретизации (создания экземпляра) компонента; 7. оператор generate (генерации); 8. оператор block (блок).

Слайд:Параллельный оператор process

Оператор процесса есть параллельный оператор, который определяет независимое последовательное поведение некоторой части проекта, описанное упорядоченной совокупностью последовательных операторов.

Метка процесса необязательна, однако если она есть в конце (после слов end process), то она должна быть и вначале перед словом process.

Общий вид оператора process (процесс)

[имя процесса :] [postponed] process [(список чувствительности)] раздел деклараций begin упорядоченное множество последовательных операторов end process [имя процесса];

В декларативной части процесса могут быть:

- тела подпрограмм;

- декларации подтипов;

- декларация констант;

- декларация файлов;

- декларация альтернативных точек входа в подпрограмму;

- декларация атрибутов;

- спецификации атрибутов.

! Процесс может иметь список сигналов запуска и один (или более) операторов ожидания, но не оба вместе.

! Сигналы не могут быть декларированы внутри процессов.

! Ожидание (wait) в начале процесса не эквивалентно ожиданию в списке чувствительности процесса.

Слайд:Оператор assert (сообщение)

Операторы сообщений проверяют, является ли условие истинным (TRUE), и сообщают об ошибке, если условие является ложным. По умолчанию сообщенное выражение есть "Assertion violation" (нарушение).

Выражение с ключевым словом severity (severity – степень серьезности) имеет перечислимый тип: NOTE, WARNING, ERROR, FAILURE.

Оператор assert может быть использован как в качестве параллельного оператора, так и в качестве последовательного оператора

Общий вид оператора assert

assert условие [report выражение ] [severity выражение ];

Примеры:

assert (CLK'event and CLK='0') report "D hold error" severity WARNING; assert (CLK'last_event > HOLD) report "D hold error" severity ERROR;

В данных примерах атрибут CLK'last_event имеет тип TIME и возвращает время, пройденное с момента последнего изменения сигнала CLK, HOLD – имеет тип TIME. Условие CLK'last_event>HOLD может быть либо истинным, либо ложным.

Слайд:Оператор параллельного вызова процедуры

Оператор параллельного вызова процедуры представляет процесс, содержащий оператор последовательного вызова процедуры. Его выполнение эквивалентно оператору процесса. Иначе говоря, процедуры могут вызываться параллельно.

Общий вид оператора

[метка:] оператор вызова процедуры

Пример:

6 architecture RTL of call_parallel is 7 procedure N_XOR ( signal x1, x2, x3 : in bit; 8 signal f : out bit) is 9 begin 10 f <= x1 xor x2 xor x3; 11 end N_XOR; 12 begin 13 N_XOR (x1=> data_inp(5), x2 => data_inp(4), x3 => data_inp(3), f => data_out(1)); 14 p0 : N_XOR (data_inp(2), data_inp(1), data_inp(0), data_out(0)); 15 end RTL;

! Каждый формальный параметр процедуры должен быть типа константы или сигнала.

Слайд:Параллельный оператор условного назначения сигнала

Oператор параллельного назначения сигнала эквивалентен оператору процесса, назначающему значения сигналам.

Могут быть употреблены опции guarded (охраняемый) transport (транспортный).

Общий вид оператора

[guarded][transport]

{назначение сигнала when условие else} сигнал;

Пример, показывающий эквивалентность параллельного оператора условного назначения сигнала (архитектурное тело first) и оператора процесса (архитектурное тело second).

entity example_condition is port ( x1, x2, x3, x4 : in bit; condition : in bit_vector(1 downto 0); F : out bit); end example_condition; architecture first of example_condition is begin F <= x1 when condition = "00" else x2 when condition = "01" else x3 when condition = "10" else x4; end first; architecture second of example_condition is begin process (x1, x2, x3, x4, condition ) begin if (condition = "00") then F <= x1; elsif (condition = "01") then F <= x2; elsif (condition = "10") then F <= x3; else F <= x4; end if; end process; end second;

Выполняться назначение для первого выполненного условия.

Слайд:Параллельный оператор select выборочного назначения сигнала

Общий вид оператора select (выбирать)

with выражение select

имя сигнала <= [guarded][transport]

{имя сигнала when условие выбора, }

имя сигнала условие выбора;

Пример, показывающий эквивалентность параллельного оператора выборочного назначения сигнала (архитектурное тело first) и оператора процесса (архитектурное тело second)

entity example_selection is port ( x1, x2, x3, x4 : in bit; selection : in bit_vector(1 downto 0); F : out bit); end example_selection; architecture first of example_selection is begin with selection select F <= x1 when "00", x2 when "01", x3 when "10", x4 when others; end first; architecture second of example_selection is begin process (x1, x2, x3, x4, selection) begin case selection is when "00" => F <= x1; when "01" => F <= x2; when "10" => F <= x3; when others => F <= x4; end case; end process; end second;

Слайд:Параллельный оператор конкретизации компонента

Этот оператор употребляется для структурной организации проекта. Часть схемы (подсхема) описывается как компонент (component), имеющий имя (name).

Одна и та же подсхема может входить в схему несколько раз, однако при этом она имеет различные связи.

Чтобы описать эти связи, употребляется оператор создания экземпляра компонента (оператор конкретизации компонента), т.е. имеется в виду конкретизация связей данной подсхемы.

Общий вид оператора конкретизации компонента (оператора создания экземпляра компонента)

метка : имя компонента

[generic (список параметров);]

[port map (список портов)];

Соответствие портов при создании экземпляров компонентов может быть осуществлено позиционным сопоставлением и ключевым соответствием, с использованием оператора "=>"

Пример

p1: A port map (x1 => x1, y1 => w) ; -- ключевое соответствие p2: B port map (w, z) ; -- позиционное соответствие p3: C port map (y3 => v, x3 => z) ; -- ключевое соответствие

Слайд:Параллельные процессы, их выполнение на ЭВМ

Каждый параллельный процесс может быть в одном из трех состояний:

- выполняющийся – когда система моделирования выполняет процесс;

- активный – когда процесс является ожидающим, чтобы система моделирования его выполнила;

- приостановленный – когда он не является выполняющимся или активным.

В реальной системе процессы могут протекать параллельно (одновременно в различных элементах). В ЭВМ общего назначения параллелизм имитируется программно.

Поэтому только один процесс из нескольких параллельных процессов является "выполняющимся" по существу. Реализация параллельных процессов происходит следующим образом.

Параллельные процессы, которые надо выполнять "одновременно", выстраиваются в очередь. Система моделирования выбирает процесс из очереди активных процессов и выполняет процесс,

тем самым исполняет предложения языка VHDL, относящиеся к данному процессу. Другие активные процессы выбираются поочередно. Заметим, что выполненный процесс является приостановленным.

Когда очередь активных процессов пуста, считается, что все параллельные процессы выполнились "одновременно", и может начаться следующий цикл моделирования.

Приостановленный процесс может стать активным, когда изменился хотя бы один из драйверов сигналов из списка чувствительности этого процесса.

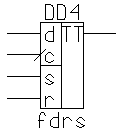

Слайд:Пример моделирования схемы, описанной на языке VHDL

Рассмотрим простую двухуровневую логическую схему и ее описание в языке VHDL в виде параллельных процессов.

entity ANDOR is port( x1, x2, x3 : in bit; f : out bit); end ANDOR; architecture example of ANDOR is signal w : bit; begin p0 : w <= x1 and x2 after 10 ns; p1 : process (w, x3) begin f <= w or x3 after 20 ns; end process p1; end example;

Во время фазы инициализации каждый сигнал из множества {x1,x2,x3} имеет значение 0. Затем, если в начальный момент времени сигналы x1, x2 и x3 изменятся, то начнёт выполняться процесс p0, поскольку цикл моделирования начинается, когда хотя бы один из сигналов изменится.

В процессе p0 будет вычислено w и процесс p0 приостановится. Затем вычисляется значение f через 30ns, так как 10ns выполняется процесс p0 и 20ns – процесс p1.

Временная диаграмма изображена на рисунке ниже.

Заметим, что если сигнал x1 при декларации не имеет начального значения, то по умолчанию он принимает значение левой границы (x1'left) декларируемого типа. Например,

signal I: integer range 0 to 3; -- при инициализации значение 0; signal X : std_logic; -- при инициализации значение 'U'.

Слайд:Дельта-задержки сигналов

Изменим архитектурное тело example для entity ANDOR, удалив ключевые слова after и конкретные временные задержки, – тем самым логические операции and, or будут срабатывать "мгновенно".

architecture DELTA_example of ANDOR is signal w : bit; begin p0 : w <= x1 and x2; -- нет слова after p1 : process (w, x3) begin f <= w or x3; -- нет слова after end process p1; end DELTA_example;

|

|

|---|

В 80 ns входной сигнал x2 изменился, что послужило причиной изменения сигнала w и причиной изменения сигнала f. Эта ситуация очерчена лупой на временной диаграмме выше.

Все это случилось точно в то же время. Рассмотрим более подробно, что же произошло в момент времени 80 ns. В 80ns входной сигнал x2 изменяется.

Начинается цикл моделирования. Активизируется процесс p0, выполняется, приостанавливается. Сигнал w изменяется в 0. Резонно сказать, что сигнал w изменился после сигнала x2.

Мы будем ссылаться на время между изменениями этих сигналов как на время дельта, или дельта-задержку.

Изменение сигнала w служит причиной для процесса p1, который активизируется, выполняется, приостанавливается. Сигнал f изменяется после изменения сигнала w.

Появляется другая дельта-задержка. В системах моделирования обычно на временных диаграммах дельта-задержки не показываются.

Например, в системе моделирования ModelSim их можно видеть в специальном окне текстового (табличного) представления результатов моделирования.

Слайд:Дельта-задержки сигналов

Понятие дельта-задержки есть основное понятие моделирования в языке VHDL.

В одно и то же время (физическое) много сигналов могут изменяться и много процессов могут быть активными.

После того как все процессы пришли в состояние "приостановленный", система моделирования увеличивает время моделирования.

Итак, ответом на вопрос "Что представляет собой дельта-задержка, или просто дельта?" является следующее:

! Дельта – это один цикл прогона VHDL-модели.

VHDL-модель, имитирующая поведение цифровой системы, состоит из множества процессов.

Во время прогона модели в данном цикле запускаются все процессы, входные параметры которых изменились с момента выполнения последнего цикла.

После того как все процессы выполнены, данный цикл моделирования считается завершенным.

Следующий цикл начнется после того, как в очередной раз произойдет изменение какого-то входного сигнала для какого-то процесса.

Этот период может составлять наносекунды времени моделирования или может просто означать, что мы перешли на следующий цикл моделирования, т.е. сделали временной шаг дельта.

Шаг величиной дельта образуется, например, при выполнении операторов назначения сигналов (в рассмотренном примере это сигналы w, f), не имеющих фразы after.

С точки зрения логической схемы дельта – это задержка на одном уровне (каскаде) логики, когда не задана конкретная задержка логического элемента.

Слайд:Параллельный оператор block

Оператор блока определяет часть проекта (часть VHDL-описания цифровой системы, схемы).

Блок – это ограниченный фрагмент VHDL-кода, содержащий раздел описания и исполняемый раздел.

Блоки могут быть иерархически вложены и поддерживать тем самым декомпозицию проекта.

Общий вид оператора block (блок)

имя блока (метка): block[(охранное выражение)]

заголовок блока

раздел деклараций

begin

параллельные операторы

end block[имя блока];

! Метка необходима в операторе блока.

В разделе деклараций блока размещаются

- декларации подпрограмм;

- тела подпрограмм;

- типы, подтипы;

- константы;

- сигналы;

- альтернативные точки входа в подпрограмму;

- декларации атрибутов;

- декларации констант;

- спецификации атрибутов;

- конфигурации.

Параллельные операторы размещаются в теле блока. Блоки могут быть вложены.

architecture XX of SYSTEM is - - - - -- раздел описаний внешнего блока - - - - - - - - begin -- выполнимые операторы внешнего блока - - - - - - - - A: block - - - - -- раздел описаний внутреннего блока A - - - - begin -- выполнимые операторы внутреннего блока A - - - - - - - - end block A; B: block - - - - -- раздел описаний внутреннего блока B - - - - begin -- выполнимые операторы внутреннего блока B - - - - - - - - end block B; end XX;

Слайд:Параллельный оператор block / охранное выражение

Обсудим теперь охранные выражения блоков. Рассмотрим архитектурное тело add1_e одноразрядного сумматора в виде охраняемого блока.

entity add1_e is port (b1,b2,enable : in BIT; c1,s1 : out BIT); end add1_e; architecture struct_3 of add1_e is begin p0: block (enable = '1') begin s1<= guarded (b1 xor b2); c1<= guarded (b1 and b2); end block p0; end struct_3;

Охранным выражением блока является выражение enable = 1. Если это выражение принимает значение true (истина), то охраняемые конструкции (назначения сигналов) выполняются, т.е. одноразрядный сумматор складывает числа, если же значение выражения является false (ложь), то охраняемые назначения сигналов не выполняются, т.е. сумматор не складывает числа b1, b2. Охрана назначения сигналов осуществляется указанием ключевого слова guarded.

Слайд:Базовые цифровые устройства

- Логические элементы (И, ИЛИ, НЕ, Исключающее ИЛИ)

- Комбинационные схемы:

- Дешифратор /Шифратор

- Мультиплексор/Демультиплексор

- Сумматор

- Компаратор

- Последовательностные схемы

- Триггеры

- Синхронные

- по фронту

- по уровню

- Асинхронные

- Синхронные

- Регистры

- Автоматы

- Счетчики

- Триггеры

Слайд:Дешифратор (VHDL модель)

entity dc is port ( x : in std_logic_vector(2 downto 0); y : out std_logic_vector(7 downto 0)); end dc; architecture beh of dc is begin y <= "00000001" when x = "000" else "00000010" when x = "001" else "00000100" when x = "010" else "00001000" when x = "011" else "00010000" when x = "100" else "00100000" when x = "101" else "01000000" when x = "110" else "10000000" when x = "111" else "00000000"; end beh;

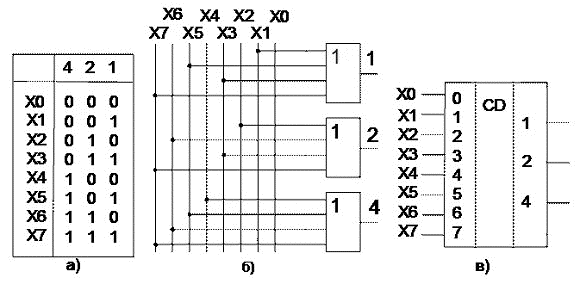

Слайд:Шифратор

- комбинационная схема, выполняющее преобразование одноединичный (позиционного) n-разрядного кода в m-разрядный двоичный код.

|

|---|

Слайд:Шифратор (VHDL модель 1)

| VHDL модель 1 | VHDL модель 2 |

|---|---|

entity cd is port ( x : in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0)); end dc; architecture beh1 of cd is begin y <= "000" when x(0) = "1" else "001" when x(1) = "1" else "010" when x(2) = "1" else "011" when x(3) = "1" else "100" when x(4) = "1" else "101" when x(5) = "1" else "110" when x(6) = "1" else "111" when x(7) = "1" else "000"; end beh1; |

entity cd is port ( x : in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0)); end dc; architecture beh2 of cd is begin y(0) <= x(1) or x(3) or x(5) or x(7); y(1) <= x(2) or x(3) or x(6) or x(7); y(2) <= x(4) or x(5) or x(6) or x(7); end beh2; |

Слайд: Мультиплексор

- комбинационная схема, которая передает сигнал с одного из информационных входов Xi на единственный выход Y, причем номер выбираемого входа задается с помощью управляющих сигналов (адресных входов ai).

|

|---|

| y = OE(x0*a1*a0 + x1*a1*a0 + x2*a1*a0 + x3*a1*a0) |

Слайд:Мультиплексор (Схема)

|

|---|

|

Слайд:Мультиплексор (VHDL модель)

entity mux is port ( x : in std_logic_vector(3 downto 0); a : in std_logic_vector(1 downto 0); y : out std_logic); end mux; architecture beh of mux is begin y <= x(0) when a = "00" else x(1) when a = "01" else x(2) when a = "10" else x(3) when a = "11" else '0'; end beh;

Слайд:Мультиплексор (Особенность)

- с помощью мультиплексора можно реализовать любую логическую функцию

|

|---|

Слайд: Демультиплексор

- комбинационная схема, которая выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Ai направляет информацию с единственного входа D на один из M выходов Fj. При этом на остальных выходах будут логические нули (единицы).

| Входы | Выходы | ||||

|---|---|---|---|---|---|

| A1 | A0 | F3 | F2 | F1 | F0 |

| 0 | 0 | 0 | 0 | 0 | D |

| 0 | 1 | 0 | 0 | D | 0 |

| 1 | 0 | 0 | D | 0 | 0 |

| 1 | 1 | D | 0 | 0 | 0 |

Слайд: Демультиплексор (Схема)

|

|

|

|---|

Слайд: Демультиплексор (VHDL модель)

entity dms is port ( x : in std_logic; a : in std_logic_vector(1 downto 0); y : out std_logic_vector(3 downto 0)); end dms; architecture beh of dms is begin y <= "000" & x when a = "00" else "00" & x & '0' when a = "01" else '0' & x & "00" when a = "10" else x & "000" when a = "11" else "0000"; end beh;

Слайд: Классификация триггеров

Ссылки:

Слайд: УГО триггеров

Слайд: VHDL-минимум для описания триггеров (1)

- Атрибуты — это различные характеристики объектов VHDL

| Атрибут | Описание |

|---|---|

| S'active | TRUE, если было присвоение, но текущее значение еще прежнее |

| S'delayed(t) | Значение сигнала, существовавшее на время t перед вычислением данного атрибута |

| S'event | TRUE, если происходит изменение сигнала |

| S'last_active | Время от последнего присвоения значения сигналу до момента вычисления атрибута |

| S'last_event | Время от последнего изменения сигнала до момента вычисления атрибута |

| S'last_value | Последнее присвоенное сигналу значение |

| S'stable(t) | TRUE, если не происходило изменение сигнала в течение времени t |

| S'transaction | TRUE, если происходит очередное присвоение значения сигналу |

| S'quiet | FALSE, если было присвоение, но текущее значение еще прежнее |

Слайд: VHDL-минимум для описания триггеров (2)

- задание (выделение) фронта сигнала

clock_edge ::= RISING_EDGE(clk_signal_name) или FALLING_EDGE(clk_signal_name) или clock_level and event_expr или event_expr and clock_level

clock_level ::= clk_signal_name = '0' или clk_signal_name = '1' event_expr ::= clk_signal_name'EVENT или not clk_signal_name'STABLE

- функции RISING_EDGE и FALLING_EDGE описаны для типов:

- BIT, BOOLEAN и др. (пакет STANDARD в VHDL'2008)

- std_logic, std_ulogic (std_logic_1164)

Слайд: VHDL-минимум для описания триггеров (3)

| Положительный фронт (переход 0 → 1) |

|---|

RISING_EDGE(clk_signal_name) clk_signal_name'EVENT and clk_signal_name = '1' clk_signal_name = '1' and clk_signal_name'EVENT not clk_signal_name'STABLE and clk_signal_name = '1' clk_signal_name = '1' and not clk_signal_name'STABLE |

| Отрицательный фронт (переход 1 → 0) |

|---|

FALLING_EDGE(clk_signal_name) clk_signal_name'EVENT and clk_signal_name = '0' clk_signal_name = '0' and clk_signal_name'EVENT not clk_signal_name'STABLE and clk_signal_name = '0' clk_signal_name = '0' and not clk_signal_name'STABLE |

- Все записи в столбцах эквивалентны

Слайд: VHDL-минимум для описания триггеров. Оператор Process (3)

- Оператор процесса

LABEL: process [ ( имя сигнала {, имя сигнала } ) ]

объявление в процессе

begin

последовательный оператор[ы]

end process;

- Пример

| Пример c process | Сокращённая запись |

|---|---|

entity A2 is port ( A, B : in std_logic; C : out std_logic); end A2; architecture beh of A2 is begin process (A, B) begin C <= A and B; end process; end beh; |

entity A2 is port ( A, B : in std_logic; C : out std_logic); end A2; architecture beh of A2 is begin C <= A and B; end beh; |

Слайд: VHDL-минимум для описания триггеров. Оператор if

- Оператор условия if (последовательный оператор)

if Условие_1 then Выражение1 elsif Условие_2 then Выражение2 else Выражение3 end if;

| Пример 1 | Пример 2 |

|---|---|

IF (s0='0' AND s1='0') THEN output <= in0; ELSIF (s0='1' AND s1='0') THEN output <= in1; ELSE output <= 'X'; END IF; |

IF (s0='0' AND s1='0') THEN output <= in0; ELSE output <= 'X'; END IF; |

| Пример 3 | Пример 4 |

IF (s0='0' AND s1='0') THEN output <= in0; ELSIF (s0='1' AND s1='0') THEN output <= 'X'; END IF; |

IF (s0='0' AND s1='0') THEN output <= in0; END IF; |

Слайд: VHDL-минимум для описания триггеров (4)

| D-Триггер без сброса |

|---|

DFF: process(CLOCK) begin if CLOCK'EVENT and CLOCK = '1' then Q <= D; -- тактироваие передним фронтом end if; end process; |

| D-Триггер со сбросом и установкой |

|---|

AS_DFF: process (CLOCK, RESET, SET) begin if RESET = '1' then Q <= '0'; elsif SET = '1' then Q <= '1'; elsif CLOCK'EVENT and CLOCK = '1' then Q <= D; end if; end process; |

Слайд: VHDL-модели триггеров (fdp)

- D-Триггер, синхронизируемый положительным фронтом, с парафазным выходом

library ieee; use ieee.std_logic_1164.all; entity fdp is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; q : out std_logic; qn : out std_logic); end fdp; architecture beh of fdp is begin p1 : process (c) begin if c'event and c = '1' then q <= to_x01(d) after del; qn <= not to_x01(d) after del; end if; end process p1; end beh; |

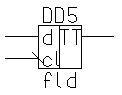

Слайд: VHDL-модели триггеров (fld)

- D-Триггер, синхронизируемый отрицательным фронтом

library ieee; use ieee.std_logic_1164.all; entity fld is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; q : out std_logic); end fld; architecture beh of fld is begin p1 : process (c) begin if c'event and c = '0' then q <= to_x01(d) after del; end if; end process p1; end beh; |

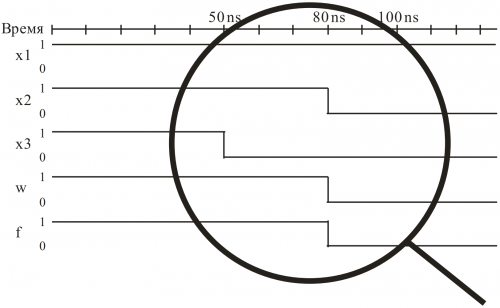

Слайд: VHDL-модели триггеров (fdrs)

- D-Триггер, синхронизируемый положительным фронтом, с асинхронным сбросом и установкой

library ieee; use ieee.std_logic_1164.all; entity fdrs is -- pragma synthesis_off generic ( del : time := 900 ps); -- pragma synthesis_on port ( d : in std_logic; c : in std_logic; r : in std_logic; s : in std_logic; q : out std_logic); end fdrs; architecture beh of fdrs is begin p1 : process (r, s, c) begin if r = '1' then q <= '0' after del; elsif s = '1' then q <= '1' after del; elsif c'event and c = '1' then q <= to_x01(d) after del; end if; end process p1; end beh; |

Слайд: Описание сдвигового регистра

entity reg is port ( di : in std_logic; d : in std_logic_vector(7 downto 0); shift_load : in std_logic; left_right : in std_logic; clk : in std_logic; -- reset reset : in std_logic; q : out std_logic_vector(7 downto 0); qi : out std_logic); end reg; architecture beh of reg is signal qq : std_logic_vector(7 downto 0); begin -- beh p1: process (clk, reset) begin -- process p1 if reset = '1' then qq(7 downto 0) <= "00000000"; -- (others => '0') elsif clk'event and clk = '1' then -- rising clock edge if shift_load = '0' then if left_right = '0' then qq <= qq(6 downto 0) & di ; qi <= qq(7); else -- left_right = '1' qq <= di & qq(7 downto 1); qi <= qq(0); end if; else -- shift_load = '1' - load mode qq <= d; end if; end if; end process p1; q <= qq; end beh;

Слайд: Счетчики. Классификация

- Счетчиком называется цифровой блок, предназначенный для подсчета входных сигналов.

- Модуль счета: число возможных состояний счетчика.