OVM/OVM методология/Основы верификации — различия между версиями

| Строка 190: | Строка 190: | ||

Для сложных последовательных конструкций, определения того, какие состояния должны быть покрыть(и какие не должны) и, как получить эти состояния с минимальными усилиями является проблемой. | Для сложных последовательных конструкций, определения того, какие состояния должны быть покрыть(и какие не должны) и, как получить эти состояния с минимальными усилиями является проблемой. | ||

| + | |||

| + | |||

| + | ===1.3.1 3-х разрядный счетчик=== | ||

| + | |||

| + | |||

| + | Схема, приведенная на рисунке 1-5, представляет собой 3-разрядный счетчик с асинхронным сбросом. Каждый раз, когда тактовый сигнал высокий, счетчик увеличивается. Схема состоит из трех переключательных триггеров, каждый из которых поддерживает один бит счета(??). Триггеры связаны с некоторой комбинационной логикой для формирования счетчика . Каждый триггер переключается, когда на входе T сигнал высокой. При низком сигнале на Т , триггер сохраняет свое текущее состояние. Когда активный низкий сброса установлен в 0, триггер переходит в состояние 0. | ||

| + | |||

| + | |||

| + | [[Файл:15.png]] | ||

| + | |||

| + | |||

| + | Код для счетчика содержится в двух модулях. Одним из них является простой переключательный триггер, а другой подключает триггера с необходимой логикой для формирования счетчика. Первый пример показывает переключательный триггер. | ||

| + | |||

| + | |||

| + | [[Файл:16.png]] | ||

| + | |||

| + | |||

| + | Счетчик состоит из трех переключательных триггеров и логического элемента И. | ||

| + | |||

| + | [[Файл:17.png]] | ||

| + | |||

| + | |||

| + | Схема проста, но имеет характеристики, которые являются общими с реальными проектами и которые требуют внимания для надлежащей проверки дизайна. Основными характеристиками является то, что конструкция работает по тактовому сигналу, и что она сохраняет внутреннее состояние. Логический элемент И из предыдущего примера не сохраняет никаких состояний. Вся информация о том, что делает схема, находится на ее входах. В конструкциях с внутренними данными, что это не так. | ||

| + | |||

| + | Эта разница отражается на схеме нашего табло. Рисунок 1-6 показывает схему testbench для 3х разрядного счетчика. | ||

| + | |||

| + | |||

| + | [[Файл:18.png]] | ||

| + | |||

| + | |||

| + | Во многих отношениях, testbench для 3-разрядного счетчика очень похож на testbench для логического элемента И. Оба имеют табло, роль которого состоит в наблюдении, что дизайн делает, и определить, выполняется ли работа правильно. Оба имеют устройства для DUT. Тем не менее, мы выполняем операции по-разному для этих конструкций. Мы используем генератор сигналов для логического элемента И, но мы используем контроллер для 3-х разрядного счетчика. 3-х разрядный счетчик автономное устройство. Пока он подключен к тактовому сигналу, он будет продолжать считать. Таким образом, нам не нужен генератор сигналов, который мы использовали для логического И. Вместо этого, контроллер управляет работой тестируемого устройства и testbench. Контроллер обеспечивает начальный сброс, так что отсчет начинается с известного значения. Он также останавливает моделирование в соответствующее время. | ||

| + | |||

| + | |||

| + | [[Файл:19.png]] | ||

| + | |||

| + | |||

| + | Табло должны отслеживать внутреннее состояние DUT. Это делается с помощью переменной count. Как и DUT, когда reset активирован, счетчик устанавливается в 0. Каждый тактовый цикл count увеличивается на единицу, и новое значение сравнивается с count, поступающего с DUT. | ||

| + | |||

| + | |||

| + | [[Файл:20.png]] | ||

| + | |||

| + | |||

| + | Табло имеет модель счетчика высокого уровня. Он использует целую переменную и оператор сложения (+) , чтобы сформировать счетчик вместо триггеров и элемента И. Каждый раз, при изменении тактового импульса, он увеличивает свой счет, так же как и RTL счетчика. Он также проверяет, соответствует ли ее внутренний счетчик выходу счетчика DUT. | ||

| + | |||

| + | Для полноты, пример показывает тактовый генератор и модуль топ-уровня. Тактовый генератор просто инициализирует тактовый сигнал 0, а затем переключает его каждые 5 нс. | ||

| + | |||

| + | |||

| + | [[Файл:21.png]] | ||

| + | |||

| + | Модуля верхнего уровня является типичным для большинства testbenches. Он соединяет DUT и компоненты testbench. | ||

| + | |||

| + | [[Файл:22.png]] | ||

| + | |||

| + | Мы показали простой testbench, который содержит элементы, используемые в гораздо более сложных testbenches. Последовательные схемы, которые поддерживают внутреннее состояние, требуют табло, которое работает параллельно с DUT. Табло выполняет те же вычисления что и DUT, но на более высоком уровне абстракции. Табло также сравнивает свои вычисления с вычислениями, полученными от DUT. | ||

Версия 13:12, 26 февраля 2013

Содержание |

1.1

Функционально проверить устройство означает, сравнить цель разработчика с полученным поведением на их эквивалентность. Мы считаем устройство проверенным, когда, к всеобщему удовлетворению, оно работает в соответствии с целью разработчика. Этот основной принцип часто теряется при использовании testbenches, среды контроля, отладки, моделирования , и все другие средства, применяемые в современных технологических проверках. Чтобы узнать, работает ли верно устройство, вы должны сравнить его с некоторыми известными эталоном, который представляет цель разработчика. Каждый testbench имеет своего рода эталонную модель и средство для сравнения функциональность устройство с эталоном.

Когда мы говорим "устройство", мы имеем в виду проверяемое устройство, часто называемое тестируемое устройство или DUT. Чтобы проверить, DUT, как правило, представлен форме подходящей для производства, которое может быть перенесено на кремний с помощью автоматизированных и ручных средств. Мы различаем DUT от эскиза на обратной стороне салфетки или окончательного нанесенный на кристалл, ни один из которых не может быть проверен. Эталонная модель отражает цели разработчика, то есть то, что устройство должно делать.Эталон может принимать различные формы, такие как документ, описывающий работу DUT, golden модель, которая содержит уникальный алгоритм, или assertions, которые представляют протокол.

Для автоматизации сравнения поведения и эталона, оба должны быть представлены в форме, которую можно выполнить на компьютере с помощью некоторых программ, что делает сравнение.

1.1.1 Два вопроса

Проверка устройства включает в себя два вопроса:Does it work? (Работает ли это устройство?) и Are we done? (Сделали ли мы?). Это основные, и некоторые сказали бы, очевидные вопросы. Тем не менее они мотивируют всю механику каждой проверочного потока. Первый вопрос - это Does it work? Этот вопрос исходит от основной идеи верификации. Он спрашивает, Соответствует ли устройство эталону? Второй вопрос - Are we done? Он спрашивает, довольны ли мы сравнительным анализом полученной схемы и эталона для определения работает ли устройство согласно цели, если нет, то почему. Мы используем эти ценные вопросы создания основы для разработки эффективных testbenches.

1.1.2 Does it work?

Does it work? Это не единственный вопрос, а категория вопросов, которые представляют природу DUT. Каждый проект будет иметь свой собственный набор Does-It-Work вопросов, чья роль заключается в определении правильного функционирования устройства. Функциональные вопросы определяют, ведет ли себя устройство должным образом в конкретных ситуациях. Мы получаем эти вопросы непосредственно из цели разработки устройства, и мы используем их, чтобы отразить цель проекта в testbench.

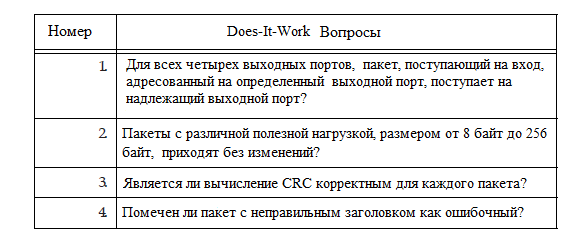

Рассмотрим простой маршрутизатор пакетов в качестве примера. Это устройство маршрутизации пакетов от входа к одному из четырех портов вывода. Пакеты содержат адреса портов назначения и имеют различные длины полезной нагрузки. Каждый пакет имеет заголовок, трейлер, и два байта для циклического избыточного кода (CRC). Does-It-Work вопросы в этом случае должны быть следующие:

- пакет, поступающий на вход порта, адресованный на имя выходного порта 3, прибыл на порт 3?

- пакет длиной 16 пришел без изменений?

- CRC байты правильны, если полезная нагрузка [0f 73 a8 c2 3e 57 11 0a 88 FF 00 00 33 2b 4c 89]?

Это простой пример полного набора вопросов. Для устройства даже такого простого как этот гипотетическое маршрутизатор, набор Does-It-Work вопросов может быть длинным. Чтобы построить план проверки и testbench, который поддерживает план, вы должны сначала перечислить все вопросы или показать как получит полный набор вопросов, а затем выберите те, которые являются интересными.

Продолжая пример маршрутизатора пакетов,для того чтобы перечислить все Does-It-Work вопросы, вы можете создать таблицу:

Приведенная выше таблица содержит два вида вопросов, те, на которые мы можем ответить сразу и те, которые мы можно разбить на более мелкие вопросы. Вопрос 1 из ряда вопросов, которые можно представить в виде:

Обратите внимание, что мы формулируем все вопросы, так что на них можно ответить да или нет. В конце концов, схема работает либо нет – она либо готова для синтеза, размещения и трассировке, либо нет. Если вы можете ответить на все вопросы утвердительно, тогда проект готов для следующего производственного шага. При разработке набора does-it-work вопросов, не забудьте сформулировать их таким образом, чтобы на них можно было ответить да или нет. Ответ да положителен, то есть, ответить да означает, что устройство работает правильно. Это будет сделать легче, чем пытаться отслеживать на какие вопросы нужно ответить да, и на какие следует ответить нет. Такой вопрос как Передает ли маршрутизатор ошибочные пакеты? требует ответа нет, чтобы считаться успешным. Лучшей формулировкой вопроса будет: Отклоняет ли маршрутизатор ошибочные пакеты? Вы должны сделать вопросы наиболее конкретными, даже если лучшее звучание будет: Когда ошибочный пакет попадает на входной порт, маршрутизатор обнаруживает его, подает сигнал ошибки и отклоняет этот пакет? Имейте в виду, что более конкретные вопросы более подробно описывают устройство. Ваш testbench должен дать ответ да или нет. Тщательно сформулированный да или нет вопрос содержит свои собственные критерии успеха. Он сообщает, что получает ответа да. Такой вопрос как, Средняя задержка менее 27 тактов? содержит метрику, 27 тактов, и форму сравнения, меньше. Если вопрос (неправильно) сформулирован, например, Какова средняя задержка прохождения пакетов через маршрутизатор? мы не будем знать, что считается приемлемым. Чтобы ответить на ваш вопрос, вы в первую очередь должны быть в состоянии определить среднее время задержки. Только при правильной постановке вопроса мы знаем, как сделать сравнение, чтобы определить, является ли результат правильным. Метрика сама по себе не говорит нам о том, функционирует ли схема как задумано. Когда мы сравниваем измеренное значение со значением в спецификации, 27 тактов в этом примере, мы можем определить, работает ли схема. Как это часто бывает, это не практично перечислять каждый does-it-work вопрос. Чтобы убедиться, что каждое слово в памяти 1 Мб можно записать и читать, непрактично и не необходимо записать один миллион вопросов. Вместо этого, вопрос-генератор, вопрос, который генерирует многие другие, занимает место миллиона отдельных вопросов. Может каждый миллион слов в памяти быть успешно записан и считан? -является вопросом-генератором. Другие вопросы могут сами по себе представлять классы вопросов. Вопрос 3, Является ли вычисление CRC корректным для каждого пакета? является примером такого вопроса. Тестирование CRC вычисления требует ряда тщательно продуманных тестов, для определения является ли вычисления CRC корректным во всех случаях.

1.1.3 Are We Done?

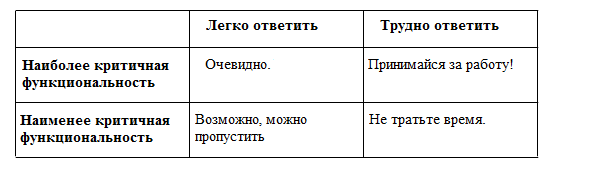

Для определения ответа на вопрос Are we done?, мы должны знать, что мы ответили на достаточное количество does-it-work вопросов, чтобы утверждать, что у нас есть проверенная схема. Мы начинаем эту задачу путем разделения на приоритеты всех does-it-work вопросов по двум направлениям:

Искусство создания testbench требует, чтобы на начальном этапе, мы определили множество вопросов и отсортировали их в соответствии с ценностью возвращаемой информации с точки зрения проверки схемы. Следующий шаг заключается в создании механизма, который будет отвечать на вопросы и определять на какие из них были даны ответы (и на какие нет).

Are-we-done вопросы также называется вопросами функционального покрытия, вопросы, которые устанавливают все ли состояния охватывают тесты с точки зрения функций схемы. Как и does-it-work вопросы, мы можем также разбить вопросы функционального охвата на более подробные вопросы. И как вопросы функциональной корректности, вопросы функционального охвата должны также иметь ответы да или нет. Приведенный ниже список включает в себя примеры вопросы функционального охвата:

• Выполняется ли каждая команда процессора, по крайней мере, один раз?

• Проходит, по крайней мере, один пакет от каждого входного порта до каждого выходного порта?

• Можно ли обратиться к памяти с набором адресов, которые содержат каждый бит адреса как 1 и затем каждый бит адреса 0, не включая 0xffffffff и 0x00000000?(?????????)

Другим мнением об этих вопросах является то, о чем они спрашивают, Получен ли утвердительный ответ на необходимый does-it-work вопрос? Когда мы думаем о функциональном охвате с этой точки зрения, то имеем виду покрытие множества does-it-work вопросов. Кроме того, вопросы охвата распознают метрику и порог для сравнения. Покрытие будет (то есть, охват вопрос можно ответить, да), когда метрика достигает порога.

Таким образом, искусство построения testbench начинается с плана тестирования. План тестирования начинается с тщательно продуманным набором does-it-work и Are-we-done вопросов.

1.1.4 Двухпетлевый поток (???????????????)

Процесс ответа на does-it-work и Are-we-done вопросы может быть описан простой схемой, как показано на рисунке 1-2. Все обусловлено функциональной спецификации на проектирование. Из функциональной спецификации, вы можете получить саму схему и план проверки. План проверки запускает testbench.

Поток состоит из двух циклов, does-it-work цикла и Are-we-done цикл. Оба цикла начинаются с моделирования. Моделирование тестирует схему при помощи testbench и генерирует информацию, которую мы используем для ответа на вопросы. Сначала мы спрашиваем, Это работает? Если ответа нет, то необходимо отладить проект. Процесс отладки схемы может привести к изменениям в реализации схемы. Как только схема работает, то пора ответить на вопрос, Are-we-done? Мы ответим на этот вопрос, собирая информацию охвата и сравнения его с порогом, указанным в тестовом плане. Если мы не достигнем порогов, то ответ нет, и мы должны изменить testbench для увеличения охвата. Тогда мы моделируем снова.

Изменение testbench или воздействия может вызвать другие скрытые ошибки в схеме. Последующие итерации по циклу могут заставить нас вернуться к does-it-work циклу снова, чтобы исправить новые ошибки, которые появятся. Как вы можете видеть, полный процесс проверки колеблется вперед и назад между does-it-work и Are-we-done циклами, пока мы не можем утвердительно ответить на все вопросы обоих категорий.

В идеальном мире, схема не имеет ошибок и с покрытием всегда полное, так что вам только надо пройти по каждому циклу один раз, чтобы получить ответы да на оба вопроса. В реальном мире, это может занять много итераций для достижения двух ответов да. Одна из целей хорошего потока проверки свести к минимуму количество итераций для выполнения верификации проекта в кратчайшие сроки с использованием наименьшего количества ресурсов.

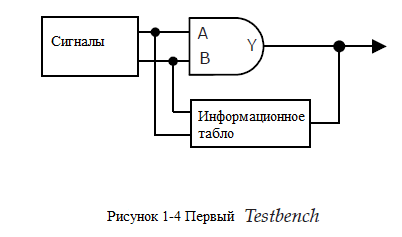

1.2 Первый Testbench

Давайте начнем с проверки одного из самых фундаментальных цифровых электронных устройств, схема логического И. Логическое И вычисляет логическое умножение входов. Функция этого устройства является тривиальной, а на практике, вряд ли должна иметь свой собственный testbench. Так как она тривиальна, мы можем использовать ее для иллюстрации некоторые основных принципов проверки без необходимости вникать в более сложную схему.

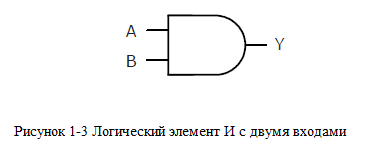

Рисунок 1-3 показывает условное обозначение логического элемента умножения с двумя входами. Логический элемент имеет два входа, А и В, и один выход Y. Устройство вычисляет логическое умножение А и В и помещает результат в Y.

Следующая таблица истинности описывает функцию устройства.

Таблица истинности является исчерпывающей: она содержит все возможные входы А и В и поэтому, все возможные значения для выхода Y.

Наша задача состоит в том, чтобы доказать, что наша схема, логического И, работает правильно. Чтобы убедиться, что он действительно выполняет функцию логического умножения правильно, нам в первую очередь необходимо перечислим вопросы. Таблица истинности поможет нам создать множество вопросов, необходимых для проверки. Каждая строка таблицы содержит вход для А и В и ожидаемый выход для Y. Так как таблица является исчерпывающей, наш вопрос-генератор будет: Для каждой ли строки в таблице истинности, когда мы получаем значения А и B, определенные в этой строке, устройство вычисляет ожидаемый результат для Y? Для ответа на Are-we-done вопрос, мы определяем, проверили ли мы каждую строку в таблице истинности, и получил ли утвердительный ответ does-itwork вопрос для этой строки. Наш Are-we-done вопрос- это Работает на всех наборах?

Для автоматизации ответов как на does-itwork та и на Are-we-done вопросы, нам нужна следующая атрибутика:

• Модель, которая представляет DUT (в данном случае, логическое И)

• Концепция конструкции в форме, которую мы можем кодифицировать как эталонную модель

• Некоторое воздействие для проверки схемы

• Способ сравнить результат с концепцией конструкции

В то время как наш маленький testbench прост, он содержит ключевые элементы, которые можно найти в большинстве testbenches любого уровня сложности. Ключевыми элементами являются следующие:

• DUT

• Генератор сигналов, который генерирует последовательность сигналов для DUT

• Табло, которое изображает эталонную модель

Табло следит за входами и выходом тестируемого устройства, выполняет же функции, что DUT за исключением более высокого уровня абстракции, и определяет, совпадает ли DUT и эталонная модель. Табло помогает нам ответить на does-itwork вопросы.

1.2.1 DUT

DUT- это наше логическое И с двумя входами. Мы реализуем логическое И, как модуль с двумя входами А и В, и одним выходом Y.

Генератор сигналов в этом примере создает управляемые сигналы. Каждое новое значение вычисляются в определенном порядке. Позже, мы будем смотреть на генератор случайных сигналов, которые, как следует из их названия, генерирует случайные значения.

Цель генератора сигналов - получение значений на вход DUT. Сигналы, двухбитная величина, содержащая значение для А и B. После того как он увеличивается при каждой последующей итерации, младший бит посылает на А, а старший бит на B.

1.2.2 Табло

Табло несет ответственность за ответы на does-it-work вопросы. Это следит за поведением DUT и сообщает работает ли оно корректно. Обратите внимание на то, что структура табло поразительно похожа на структуру DUT. Это имеет смысл, когда вы считаете, что назначением табло является отслеживание активности DUT и определение, работает ли DUT как ожидалось.

Табло отображает пины всех входов. На табло не вызывает воздействия на схему. Он пассивно наблюдает за входами и выходами тестируемого устройства.

Модуль верхнего уровня, как показано ниже, является полностью структурным, он содержит экземпляров тестируемого устройства, табло и генератор сигналов, с кодом, необходимым для их подключения.

Когда мы запускаем моделирования для нескольких итераций, вот что мы получаем:

Каждое сообщение состоит из двух частей. В первой части показаны применяемые сигналы. Вторая часть показывает результаты проверки табло , который сравнивает соответствие DUT с необходимыми результатами. Мы используем двоеточие для разделения двух частей.

Этот простой testbench демонстрирует использование генератора сигналов и табло, которое служит в качестве эталона. Несмотря на то, DUT – логическое И, все элементы полного testbench присутствуют.

1.3 Второй Testbench

В предыдущий пример показывает элементарные понятия проверки с использованием комбинационного дизайна. Комбинационные конструкций, по природе, не поддерживают никаких статических данных. В нашем втором примере мы рассмотрим чуть более сложную конструкцию, которая сохраняет данные о состояниях и использует тактовый сигнал для перехода между состояниями.

Проблема проверки, связанная с синхронными (последовательными) схемами, иная чем у комбинационных конструкций. Все, что вам нужно знать о комбинационной схеме доступно на ее контактах. Эталонная модель для комбинационного устройства просто должна вычислять F (X), где X представляет входы устройства и F – это реализуемая функция. Выходы же на последовательном устройстве зависят от входных сигналов и его внутреннего состояния. Дальнейшее вычисление может изменить внутреннее состояние. Табло должны отслеживать внутреннее состояние тестируемого устройства и сравнить выходные данные.

Комбинационных устройств может быть полностью проверено при подаче всех возможных сигналов на входы. Для устройств N входами, мы должны применить в общей сложности 2n входных комбинаций. Число 2n может быть большим, но вычисление такого количества входов достаточно просто. Нам просто необходимо иметь N-разрядный счетчик и посылать каждое значение счетчика на входы устройства. Для последовательного устройства, понятие "done" должно распространяться и на покрытие не только всевозможных сигналов на входах, но и на число всевозможных внутренних состояний. Для устройства с n входами и m внутренних состояний, вы должны покрыть (2n входов) * (2m внутренних состояний), 2n+m – число всевозможных комбинаций внутренних состояний и входов. Для устройства с 64 входами и одним 32-битный внутренним регистром, количество комбинаций 296 -очень большое число, не так ли!

Даже для очень большого числа комбинаций, проверка не была бы слишком трудной, если бы было возможно просто увеличивать счетчик для получения всех комбинаций, как мы делаем с комбинационными устройствами. К сожалению, это не представляется возможным. Внутреннее состояние напрямую не доступны извне устройства. Оно может быть изменено только путем манипулированием входов. И теперь проблема заключается в том, как добраться до всех состояний в устройстве только через входы. Это сложная проблема, которая требует глубокого понимания устройства, для генерации последовательности входов для получения всех состояний.

Поскольку трудно получить все состояния, становится очевидным вопрос, Можем ли мы упростить задачу путем сокращения числа состояний, которые мы должны получить, чтобы показать, что устройство работает правильно? Ответ: да. Теперь возникает другой вопрос, Как мы решим, какие состояния можно пропустить?

Эта тема является сложной. Тем не менее, мы можем дать интуитивный ответ на вопрос. Состояния, которые могут быть отмечены как недоступные, при использовании формальной проверки или других методов, не должны быть покрыты. Проектировщик должен рассмотреть вопрос об упрощении схемы для удаления недоступных состояний, так как они не представляют никакой ценности. Состояния, которые имеют низкую вероятность быть достигнутыми, также могут быть исключены из плана проверки. Определение порогового значения вероятности и вероятностей состояний такое же искусство, как наука. Она включает в себя понимание того, как устройство используется и какие входы необходимы (по сравнению с которые возможны).

Это также позволяет устранить состояния, которые являются функционально эквивалентными. Рассмотрим устройство пакет коммуникаций. В теории, каждое возможное значение полезной нагрузки пакета представляет собой различное состояние (или множества состояний), которое принимает схема, и оно должно быть покрыто во время проверки. Однако, это, вероятно, не будет преувеличением считать, что произвольное ненулевое значение, для всех намерений и целей, эквивалентно. Конечно, могут быть некоторые интересные случаи, которые должны быть проверены, как все нули, все единицы, конкретные значения, которые могли бы бросить алгоритмы коррекции ошибок, и так далее. Изменения данных становятся интереснее, когда они влияют на поток управления.

В общем, это более важно, чтобы охватить управляющие состояния, чем состояние данных. Простым способом уменьшить число состояний, необходимых для покрытия схемы является разделения данных и управления. Для конкретного пути контроля, данные могут быть произвольными. По некоторых данных, вы можете захотеть изменить путь управления. Например, в ALU вы можете разделить функции контроля записи данных и получения данных из регистров и установление арифметической операции для выполнения из результатов конкретные арифметических операций. Использование направленного управления, вы можете сделать данные случайные или рассмотреть данные в специфичных случаях, таких как деление на 0 или умножение на 1.

Для сложных последовательных конструкций, определения того, какие состояния должны быть покрыть(и какие не должны) и, как получить эти состояния с минимальными усилиями является проблемой.

1.3.1 3-х разрядный счетчик

Схема, приведенная на рисунке 1-5, представляет собой 3-разрядный счетчик с асинхронным сбросом. Каждый раз, когда тактовый сигнал высокий, счетчик увеличивается. Схема состоит из трех переключательных триггеров, каждый из которых поддерживает один бит счета(??). Триггеры связаны с некоторой комбинационной логикой для формирования счетчика . Каждый триггер переключается, когда на входе T сигнал высокой. При низком сигнале на Т , триггер сохраняет свое текущее состояние. Когда активный низкий сброса установлен в 0, триггер переходит в состояние 0.

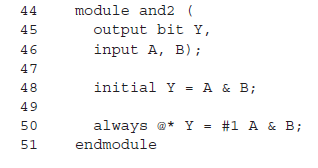

Код для счетчика содержится в двух модулях. Одним из них является простой переключательный триггер, а другой подключает триггера с необходимой логикой для формирования счетчика. Первый пример показывает переключательный триггер.

Счетчик состоит из трех переключательных триггеров и логического элемента И.

Схема проста, но имеет характеристики, которые являются общими с реальными проектами и которые требуют внимания для надлежащей проверки дизайна. Основными характеристиками является то, что конструкция работает по тактовому сигналу, и что она сохраняет внутреннее состояние. Логический элемент И из предыдущего примера не сохраняет никаких состояний. Вся информация о том, что делает схема, находится на ее входах. В конструкциях с внутренними данными, что это не так.

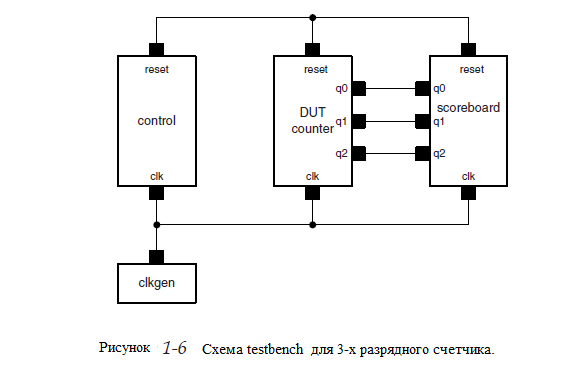

Эта разница отражается на схеме нашего табло. Рисунок 1-6 показывает схему testbench для 3х разрядного счетчика.

Во многих отношениях, testbench для 3-разрядного счетчика очень похож на testbench для логического элемента И. Оба имеют табло, роль которого состоит в наблюдении, что дизайн делает, и определить, выполняется ли работа правильно. Оба имеют устройства для DUT. Тем не менее, мы выполняем операции по-разному для этих конструкций. Мы используем генератор сигналов для логического элемента И, но мы используем контроллер для 3-х разрядного счетчика. 3-х разрядный счетчик автономное устройство. Пока он подключен к тактовому сигналу, он будет продолжать считать. Таким образом, нам не нужен генератор сигналов, который мы использовали для логического И. Вместо этого, контроллер управляет работой тестируемого устройства и testbench. Контроллер обеспечивает начальный сброс, так что отсчет начинается с известного значения. Он также останавливает моделирование в соответствующее время.

Табло должны отслеживать внутреннее состояние DUT. Это делается с помощью переменной count. Как и DUT, когда reset активирован, счетчик устанавливается в 0. Каждый тактовый цикл count увеличивается на единицу, и новое значение сравнивается с count, поступающего с DUT.

Табло имеет модель счетчика высокого уровня. Он использует целую переменную и оператор сложения (+) , чтобы сформировать счетчик вместо триггеров и элемента И. Каждый раз, при изменении тактового импульса, он увеличивает свой счет, так же как и RTL счетчика. Он также проверяет, соответствует ли ее внутренний счетчик выходу счетчика DUT.

Для полноты, пример показывает тактовый генератор и модуль топ-уровня. Тактовый генератор просто инициализирует тактовый сигнал 0, а затем переключает его каждые 5 нс.

Модуля верхнего уровня является типичным для большинства testbenches. Он соединяет DUT и компоненты testbench.

Мы показали простой testbench, который содержит элементы, используемые в гораздо более сложных testbenches. Последовательные схемы, которые поддерживают внутреннее состояние, требуют табло, которое работает параллельно с DUT. Табло выполняет те же вычисления что и DUT, но на более высоком уровне абстракции. Табло также сравнивает свои вычисления с вычислениями, полученными от DUT.